# Application Note OA-12, Rev. B Noise Design of Current-Feedback Op Amp Circuits

Kumen Blake

April 1996

## Abstract

This App Note covers the noise model for all currentfeedback op amps, simple design techniques and useful approximations. This is a frequency-domain model to simplify circuit analysis and design. This information simplifies the selection of a low-noise current-feedback op amp.

This revision obsoletes the previous revision of this App Note, and covers additional material.

## Contents

The subjects covered are:

- The noise model for current-feedback op amps

- Converting noise densities to integrated noise

- Interpreting integrated noise as SNR

- Output noise improvement

- 1/f noise calculations

- SPICE models

- A design example

- A derivation of the Noise Power Bandwidth approximation (Appendix A)

- A bibliography (Appendix B)

## Scope of Noise Analysis

The noise analysis in this App Note deals with random noise generated by the devices and components in a circuit. Noise analysis gives the greatest benefit when:

- The signal level is low

- The signal to noise ratio (SNR) is high

- The signal sees a substantial gain

Noise analysis will not help:

- Identify and eliminate oscillation or instability problems

- Reduce EMI (Electro-Magnetic Interference)

- Reduce cross talk

## **Noise Model**

Three input-referred noise density (spot noise) sources model the noise generated by current-feedback (CFB) op amps. Noise power density ( $e_n^2$  or  $i_n^2$ ) is the power measured in a narrow bandwidth, normalized to the load resistance, in units of V<sup>2</sup>/Hz or A<sup>2</sup>/Hz. Voltage noise density ( $e_n$ ) and current noise density ( $i_n$ ) are the square-root of noise power density in units of V/ $\sqrt{Hz}$  or A/ $\sqrt{Hz}$ . Notice that these noise densities are functions of frequency.

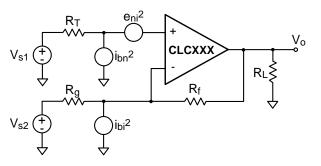

Figure 1 shows the three input noise density sources,  $e_{ni}^2$ ,  $i_{bn}^2$  and  $i_{bi}^2$ , in a standard amplifier circuit. The specifications give densities that are constant over frequency (white noise). Ground  $R_T$  for inverting gain circuits, and ground  $R_q$  for non-inverting gain circuits.

## Figure 1: CFB Noise Model

The equation for the output voltage noise density is:

$$\begin{split} \mathbf{e}_{no}^{2} &= \mathbf{G}_{n}^{2} \cdot \left( \mathbf{e}_{ni}^{2} + \left( \mathbf{i}_{bn} \mathbf{R}_{T} \right)^{2} + 4kT \left( \mathbf{R}_{T} + \left( \mathbf{R}_{f} \mid \mid \mathbf{R}_{g} \right) \right) \right) \\ &+ \left( \mathbf{i}_{bi} \mathbf{R}_{f} \right)^{2} + \left( \mathbf{e}_{ns1} \mathbf{G}_{n} \right)^{2} + \left( \mathbf{e}_{ns2} \left( \mathbf{G}_{n} - 1 \right) \right)^{2} \end{split}$$

where:

- $\bullet G_n = 1 + \frac{R_f}{R_g}$

- $e_{no}$  is the voltage noise density (V/ $\sqrt{Hz}$ ) seen at V<sub>o</sub>

- e<sub>ni</sub> is the op amp's input voltage noise density (V/√Hz)

- i<sub>bn</sub> and i<sub>bi</sub> are the op amp's input current noise densities (A/√Hz)

- $4kT = (16.0 \times 10^{-21} \text{J}) \cdot \frac{\text{T}}{290^{\circ}\text{K}}$ , T is the temperature in °K

- $e_{ns1}$  and  $e_{ns2}$  are the voltage noise densities (V/ $\sqrt{Hz}$ ) produced by V<sub>S1</sub> and V<sub>S2</sub>

The load resistor  $(R_L)$  has a negligible contribution to the noise because the output resistance of the op amp is very small.

The system transfer function will shape the output noise. See **References** [1 & 2] in **Appendix B** for information on how to generate noise transfer functions. The **1/f Noise** section covers excess noise (noise that exceeds the white noise specifications).

#### Integrated Noise

Convert the output voltage noise density to the integrated output voltage noise by integrating over frequency:

$$\mathsf{E}_{\mathsf{no}} = \sqrt{\int_{0}^{\infty} \mathsf{e}_{\mathsf{no}}^{2} |\mathsf{H}_{\mathsf{eno}}(\mathsf{jf})|^{2}} d\mathsf{f} = \mathsf{e}_{\mathsf{no}} \cdot \sqrt{\mathsf{NPBW}}$$

NPBW  $\approx 1.3 \cdot f_2 - 0.8 \cdot f_1$

where:

- H<sub>eno</sub>(jf) is the noise transfer function for eno

- f<sub>1</sub> is the lower -3dB corner frequency for ACcoupled systems, or the lowest frequency that affects your system's performance

- f<sub>2</sub> is the upper -3dB corner frequency

- The NPBW (Noise Power Bandwidth) approximation holds when: • there is  $\leq$  3dB of gain peaking

- f<sub>1</sub> << f<sub>2</sub>

- If the NPBW approximation does not hold, use numerical integration instead

The integrated output noise, Eno, is the standard deviation of the output noise in units of  $V_{\mbox{rms}}.$  It is also a measure of the lower end of the useful dynamic range. Because integrated output noise depends on the circuit architecture, component values and the op amp, it is best to compare op amps based on the input noise densities.

To see how each noise source contributes to  $E_{no}$ , integrate each term separately:

$$\mathsf{E}_{no}^{2} = \int_{0}^{\infty} \mathsf{G}_{n}^{2} \mathsf{e}_{ni}^{2} \left| \mathsf{H}_{eni}\left(\mathsf{jf}\right) \right|^{2} \mathit{d}\mathsf{f} + \int_{0}^{\infty} \mathsf{G}_{n}^{2} \mathsf{i}_{bn}^{2} \mathsf{R}_{\mathsf{T}}^{2} \left| \mathsf{H}_{ibn}\left(\mathsf{jf}\right) \right|^{2} \mathit{d}\mathsf{f} + \dots$$

This information is useful for improving the amplifier's SNR.

#### **Dynamic Range**

Signal to noise ratio (SNR) describes how much dynamic range a signal has. It compares the lower end of the useful dynamic range (Eno) to the signal magnitude (in units of V<sub>rms</sub>). The input and output signal to noise ratios are:

$$\begin{split} & \text{SNR}_{\text{in}} = 20 \text{log} \Bigg( \frac{\text{V}_{\text{in}(\text{rms})}}{\text{E}_{\text{nin}}} \Bigg), \text{dB} \\ & \text{SNR}_{\text{o}} = 10 \text{log} \Bigg( \frac{\text{V}_{\text{o}(\text{rms})}^2/\text{R}_{\text{L}}}{\text{E}_{\text{no}}^2/\text{R}_{\text{L}}} \Bigg) = 20 \text{log} \Bigg( \frac{\text{V}_{\text{o}(\text{rms})}}{\text{E}_{\text{no}}} \Bigg), \text{dB} \end{split}$$

where:

- V<sub>in(rms)</sub> is the signal voltage at the input  $(V_{S1} \text{ or } V_{S2}), V_{rms}$

- Enin is the integrated voltage noise at the input (at  $V_{S1}$  or  $V_{S2}$ ),  $V_{rms}$

- V<sub>o(rms)</sub> is the signal voltage at the output, V<sub>rms</sub>

E<sub>no</sub> is the integrated voltage noise at the output, V<sub>rms</sub>

### Improving Output Noise

To reduce output noise, do the following:

- Band-limit the signal after the op amp to limit the final output noise

- AC couple when possible

- Use a low-pass filter, or a band-pass filter

- Reduce gain peaking to lower the NPBW

- Reduce resistor values to lower thermal noise,

- but keep in mind that:

- R<sub>f</sub> values smaller than that recommended in the datasheet will cause gain peaking and increased bandwidth; the NPBW may increase

- faster than the intended noise reduction

- Smaller loads at the op amp's output increase distortion and power consumption

- Resistors connected to the input of currentsensing amplifiers act as current noise sources; increase these resistor values to reduce thermal noise

For those op amps with an adjustable supply current, the input noise sources change with supply current. As the supply current increases, the input voltage noise decreases, the input current noises increase, the distortion improves and the bandwidth increases. For the best voltage noise performance, use the highest supply current. For the best current noise performance, use the lowest supply current.

#### 1/f Noise

At low frequencies, the three input noise density terms are larger than predicted by the specifications. The dominant source of this excess noise is 1/f (or flicker) noise. Burst noise also contributes to excess noise, but is not covered in this App Note. The input noise sources, with both the 1/f noise and white noise terms included, are:

$$\begin{split} e_{ni}^2(f) &= e_{ni}^2\left(1 + \frac{f_{c(eni)}}{f}\right) \\ i_{bn}^2(f) &= i_{bn}^2\left(1 + \frac{f_{c(ibn)}}{f}\right) \\ i_{bi}^2(f) &= i_{bi}^2\left(1 + \frac{f_{c(ibi)}}{f}\right) \end{split}$$

where:

- $e_{ni}^2(f)$  is the sum of the white noise term,  $e_{ni}^2$ , and the 1/f noise term,  $e_{ni}^2 \cdot \frac{t_{c(eni)}}{f}$

- $f_{c(eni)}$  is the corner frequency of the 1/f noise for  $e_{ni}^{2}(f)$ ; this is the point where  $e_{ni}^{2}(f)$ doubles its white noise value

- the other input noise terms are defined similarly

Notice that flicker noise power density is proportional to 1/f; flicker voltage noise density and flicker current noise densities are proportional to  $1/\sqrt{f}$ .

To integrate both white noise and 1/f noise, evaluate individual noise terms separately. For each term we obtain:

$$\begin{split} E_n^2 &= \int_0^\infty e_n^2 \left( 1 + \frac{f_c}{f} \right) \Big| \; H_{en} \left( jf \right) \Big|^2 df = e_n^2 \cdot \text{NPBW} \\ \text{NPBW} &\approx \left( 1.3 \cdot f_2 - 0.8 \cdot f_1 \right) + \text{NPBW}_{1/f} \\ \text{NPBW}_{1/f} &\approx f_c \cdot \text{In} \left( \frac{f_2}{f_1} \right) \end{split}$$

The 1/f noise contribution is negligible when  $f_2 >> f_c$ .  $f_1$  is the largest frequency that does not affect your system's performance when the amplifier is DC-coupled.

Use metal-film resistors to minimize 1/f noise.

### **SPICE Models**

SPICE models are available for most of Comlinear's amplifiers. These models support AC noise simulations at room temperature. We recommend simulating with Comlinear's SPICE models to:

- Predict a better value for NPBW

- Support quicker design cycles

To verify your simulations, we recommend breadboarding your circuit. Evaluation boards are available for building and testing Comlinear's amplifiers.

### **Design Example**

This design example demonstrates the noise design of a simple circuit. The CFB op amp in this example is not an actual product; *the parameter values shown are arbitrary* and are for illustration purposes only.

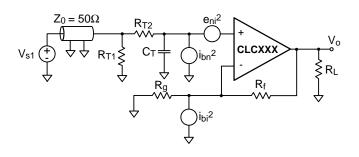

This example uses the non-inverting gain amplifier in Figure 2. The components shown are:

- V<sub>s1</sub> is the input voltage source (with very low output impedance). The signal at V<sub>s1</sub> is 100mV<sub>rms</sub>, and the voltage noise e<sub>ns1</sub> (at V<sub>S1</sub>) is 3.0nV/√Hz.

- A 50Ω coax cable is placed between the source and the amplifier

- R<sub>T1</sub> = 50Ω to match the coax cable's impedance and prevent reflections

- R<sub>T2</sub> prevents gain peaking, and filters the input signal with C<sub>T</sub>

- C<sub>T</sub> filters the input signal (this reduces the signal's slew rate)

- R<sub>f</sub> and R<sub>g</sub> set the gain; the recommended R<sub>f</sub> is 250Ω for a gain of 10

- R<sub>L</sub> is 100Ω

- The op amp noise terms are:

- $e_{ni} = 3.0$  nV/ $\sqrt{Hz}$  and  $f_{c(eni)} = 1.0$  kHz

- $i_{bn}$  = 2.0pA/√Hz and  $f_{c(ibn)}$  = 5.0kHz

- $i_{bi}$  = 12pA/√Hz and  $f_{c(ibi)}$  = 10kHz

- Ambient temperature (T) is 25°C

- Power dissipation of the op amp causes a 15°C junction temperature rise

### Figure 2: Non-Inverting Gain Amplifier

The design goals are:

- Provide a gain of 10 (=  $G_n$  for non-inverting gains)

- DC-couple the signal; the lowest frequency that affects system performance is 10Hz (f<sub>1</sub>)

- Set an upper 3dB corner frequency of 10MHz (f<sub>2</sub>)

- Achieve an output SNR of 74dB

The initial design choices we made are:

- 20MHz pole at the input set by C<sub>T</sub> and R<sub>T2</sub> (this will cause reflections in the coax cable for any signal above this pole)

- 10MHz filter after this amplifier (not shown); this will set f<sub>2</sub> (NPBW)

- R<sub>T2</sub> = 1.0kΩ

- C<sub>T</sub> = 8pF

- R<sub>f</sub> = 250Ω, its recommended value, to avoid gain peaking

- $R_q = 27.8\Omega$  to set the gain to  $G_n = 10$

The resulting junction temperature of the op amp, input integrated noise and input SNR are:

$$\begin{split} T &= 25^{\circ}C + 15^{\circ}C = 40^{\circ}C = 313^{\circ}K \\ E_{ns1} &= e_{ns1} \cdot \sqrt{NPBW} \\ &\approx \left(3.0nV/\sqrt{Hz}\right)\sqrt{13MHz - 8Hz} \\ &\approx \left(10.8\mu V_{rms}\right)^2 \\ SNR_{in} &\approx 79.3dB \end{split}$$

$R_{T1}$  does not contribute to the output noise;  $V_{S1}$  is a nearly ideal voltage source.

The input source produces an output noise of:

$$G_n^2 \cdot e_{ns1}^2 \cdot NPBW \approx (108 \mu V_{rms})^2$$

The individual white noise contributions of the op amp to the output noise are:

$$\begin{split} G_n^2 \cdot e_{ni}^2 \cdot NPBW &\approx \left(108\mu V_{rms}\right)^2 \\ G_n^2 \cdot i_{bn}^2 \cdot R_{T2}^2 \cdot NPBW &\approx \left(72\mu V_{rms}\right)^2 \\ i_{bi}^2 \cdot R_f^2 \cdot NPBW &\approx \left(11\mu V_{rms}\right)^2 \end{split}$$

The individual 1/f noise contributions of the op amp to the output noise are:

$$\begin{split} G_n^2 \cdot e_{ni}^2 \cdot NPBW_{1/f} &\approx (10)^2 \Big( 3.0 nV/\sqrt{Hz} \Big)^2 \bigg( (1 \text{kHz}) \cdot \ln \bigg( \frac{10 \text{MHz}}{10 \text{Hz}} \bigg) \bigg) \\ &\approx \big( 3.5 \mu V_{rms} \big)^2 \\ G_n^2 \cdot i_{bn}^2 \cdot R_{T2}^2 \cdot NPBW_{1/f} &\approx \big( 5.3 \mu V_{rms} \big)^2 \\ i_{bi}^2 \cdot R_f^2 \cdot NPBW_{1/f} &\approx \big( 1.1 \mu V_{rms} \big)^2 \end{split}$$

The contributions of the other components to the output noise are:

$$G_{n}^{2} \cdot 4kTR_{T2} \cdot NPBW \approx (10)^{2} (4.2nV/\sqrt{Hz})^{2} (13MHz - 8Hz)$$

$$\approx (150\mu V_{rms})^{2}$$

$$G_{n}^{2} \cdot 4kT(R_{f} ||R_{g}) \cdot NPBW \approx (24\mu V_{rms})^{2}$$

The resulting output integrated noise, output signal and output SNR are:

$$\begin{split} & \mathsf{E}_{no} \approx 227 \mu \mathsf{V}_{rms} \\ & \mathsf{V}_{o(rms)} = \mathsf{G}_n \mathsf{V}_{in(rms)} \approx 1.00 \mathsf{V}_{rms} \\ & \mathsf{SNR}_o \approx 72.9 \mathsf{dB} \end{split}$$

Reduce  $R_{T2}$  to improve SNR; this has little impact on other performance parameters. Changing  $R_{T2}$  to 200 $\Omega$  gives:

$$C_T = 40 \text{pF}$$

$E_{no} \approx 169 \mu V_{rms}$

$SNR_o \approx 75.4 \text{dB}$

In an actual design, the next step would be SPICE simulations, then breadboarding the circuit.

#### Conclusions

The important points to remember when designing low noise circuits are:

- Employ noise analysis where small signals are present

- Select correct resistor values to reduce thermal noise

- Select op amps based on their input noise densities (integrated noise is circuitdependent)

- Reduce NPBW and gain peaking to minimize integrated output noise

- Estimate your signal's dynamic range using SNR

- Simulate with Comlinear's SPICE models to estimate noise performance

- Build and measure your circuit to verify the design

- Refer to the *Bibliography* in *Appendix B* for additional background information

## Appendix A

## (derivation of Noise Power Bandwidth formula)

The goal is to estimate NPBW using common, easy to measure parameters: the -3dB bandwidth and gain

peaking. We assume a second-order transfer function for the op amp circuit's high-frequency behavior:

$$H(s) = \frac{H_{o}}{1 + \frac{1}{Q} \cdot \frac{s}{\omega_{o}} + \frac{s^{2}}{\omega_{o}^{2}}}$$

$$|H(jf)| = \frac{H_{o}}{\sqrt{1 + \left(\frac{1}{Q^{2}} - 2\right) \cdot \left(\frac{f}{f_{o}}\right)^{2} + \left(\frac{f}{f_{o}}\right)^{4}}}$$

$$s = j\omega = j2\pi f$$

where  $\omega_{o}$  =  $2\pi f_{o}$  is the natural frequency of this transfer function.

Integrating the magnitude squared of the transfer function gives:

NPBW =

$$\int_0^\infty |H(jf)|^2 df$$

=  $\frac{\pi}{2} \cdot Q \cdot f_0$

Solving for the upper -3dB corner frequency ( $f_2$ ), and substituting the result in the equation above, gives:

NPBW =

$$\frac{\frac{\pi}{2} \cdot \mathbf{Q} \cdot \mathbf{f}_2}{\sqrt{\left(1 - \frac{1}{2\mathbf{Q}^2}\right) + \sqrt{\left(1 - \frac{1}{2\mathbf{Q}^2}\right)^2 + 1}}}$$

Gain peaking is easy to measure, and is a strong function of Q for large Q. It is easy to show that:

$$Q = \frac{H_{max}}{H_o} \cdot \frac{\sqrt{1 + \sqrt{1 - \frac{H_o^2}{H_{max}^2}}}}{\sqrt{2}}, \ \frac{1}{\sqrt{2}} \le Q$$

where  $H_{max}$  is the peak gain magnitude.

These results support the following approximations:

NPBW

$$\approx (1.3) \cdot f_2$$

,  $\frac{H_{max}}{H_0} \le 1.5$

$\approx \frac{H_{max}}{H_0} \cdot f_2$ ,  $1.0 < \frac{H_{max}}{H_0}$

with a 20% maximum error. This translates to a 0.8dB maximum error in the estimated SNR.

If the amplifier transfer function has a single pole response, it is easy to show that:

NPBW =

$$\frac{\pi}{2} \cdot f_2$$

, single pole transfer function

High-order filters will have:

NPBW

$$\approx f_2$$

, high-order filters

The approximation formula includes both of these cases.

The above results hold for the lower corner -3dB frequency ( $f_1$ ) with minor modifications. When the corner -3dB frequencies do not interact ( $f_1 << f_2$ ), we obtain:

$$NPBW \approx \left(1.3 \cdot f_2 - 0.8 \cdot f_1\right), \ \frac{H_{max}}{H_o} \leq 3.0 dB$$

It is easy to extend this result when there is more than 3.0dB of peaking, but it is better to reduce the peaking, or to numerically integrate the output noise.

## Appendix B (Bibliography)

- C. D. Motchenbacher and J. A. Connelly, Low-Noise Electronic System Design, New York: John Wiley & Sons, 1993.

- P. R. Gray and R. G. Meyer,

Analysis and Design of Analog Integrated Circuits, 2nd Ed. New York: John Wiley & Sons, 1984.

- [3] J. D. Gibson, Principles of Digital and Analog Communications, New York: Macmillan, 1989.

- [4] A. B. Carlson,

Communication Systems: An Introduction to Signals and Noise in Electrical Communication, 3rd Ed. New York: McGraw-Hill, 1986.

- [5] P. Antognetti and G. Massobrio (Editors), Semiconductor Device Modeling with SPICE, New York: McGraw-Hill, 1988.

## **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation

1111 West Bardin Road

Arlington, TX 76017

Tel: 1(800) 272-9959

Fax: 1(800) 737-7018

National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support@nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.