# Why should you care about JTAG / Boundary Scan / IEEE 1149.x

GOEPEL Boundary Scan Seminar

Heiko Ehrenberg

h.ehrenberg@goepelusa.com

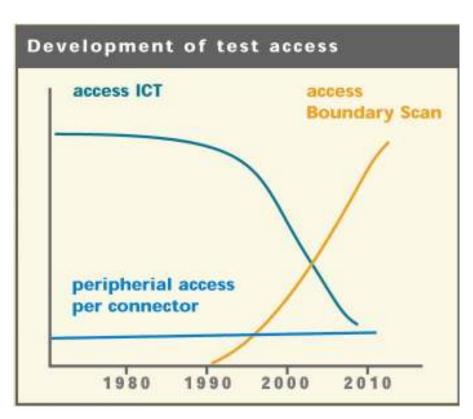

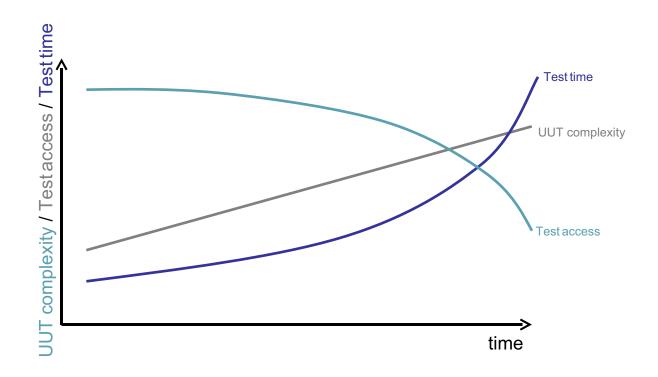

### Why do we need DFT?

- Shrinking device geometries, device pitch

- New packaging technologies

- Diminishing test access

- Rising UUT complexity

- Rising test time

#### Test obstacles

- UUT complexity

- Test access

- Test time

### **UUT** complexity

- Highly integrated components

- More functionality on one board

- Reduced testability

#### And at the same time ...

- Shorter NPI and PLC

- High product mix

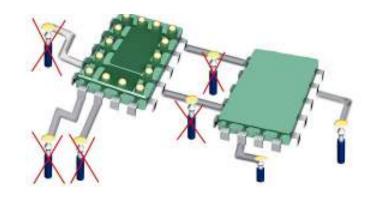

#### Reduced test access

- New device packaging (µBGA, CSP, COP, ...)

- Passive components embedded in PCB

- Denser board layouts

- Fewer, smaller test points

Diminishing test access with probe based test systems

#### Cost of Test

- Requirement to lower cost because of

- Inflation

- Shorter PLC

- Smaller profit margins

- Test DOES "add value" by

- Catching defects

- Helping control the manufacturing process

- Reducing field returns and warranty issues

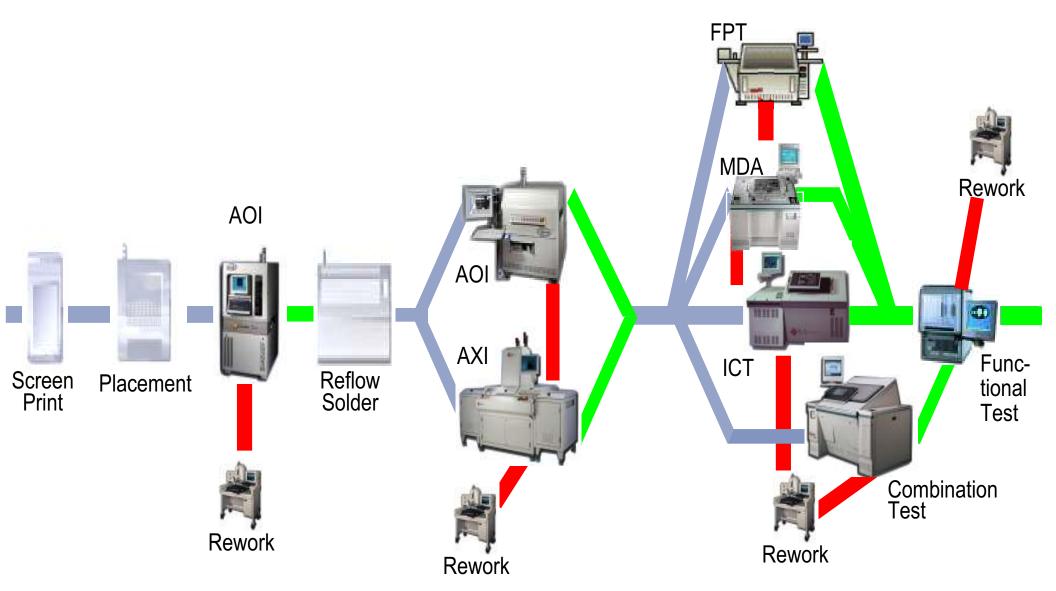

How do we test?

Automated

Optical /

X-Ray

Inspection

(AOI/AXI)

Manufacturing

Defect Analyser

(MDA)

Flying Probe Test (FPT)

Functional Test (FT)

Manual Inspection

In-Circuit Test , (ICT)

**Boundary Scan**

most likely: a combination of those methods

### Common test solutions

# Frequent problems

- High density, small footprint components (BGA, microBGA, Chip On Board, Chip Scale Packages)

- Loss of test access

- Ballooning Fixture Costs

- Long test development time

- Reduced diagnostic resolution

Is there a way out?

# Can Boundary Scan help?

- Regain test access

- Improve time to market

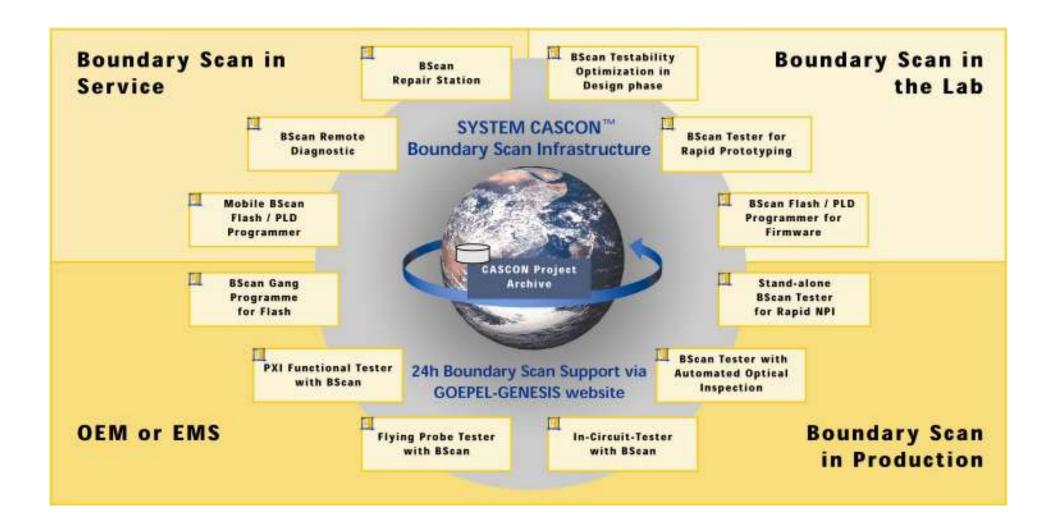

- Use Boundary Scan throughout the whole product life cycle (reuse test applications)

- Supports chip, board, and system level test

- Reduce fixture cost

- Improve diagnostic resolution

- Shorten debug time

Reduce cost of test

### Case Study A

#### Type 1: single PCB, predominantly digital circuits

- components with relatively small pin count, no BGA's;

- Some components with Boundary Scan capabilities;

- well suited for In-Circuit-Test;

- cost saving potential in combination of Boundary Scan with ICT

#### Example:

- ~ 1200 component leads

- 200 nets

- 3 BScan compliant components

- 54 BScan accessible nets (27%)

- Bed-Of-Nail adapter with 200 nails: about \$5,000 (80% of the total account for nails, or \$4,000)

- reducing the number of nails by 54 (27% of all 200 nets)

- $\Rightarrow$  achievable savings: 27% of \$4,000, or \$1,080

- 50 different kinds of such PCB's: save ~ \$54,000 annually

# Case Study B

#### Type 2: single PCB, predominantly digital circuits

- components with high pin count, few BGA's;

- Some components provide Boundary Scan capabilities;

- High product mix, low volume ⇒ Flying Prober most useful

#### Example (average unit):

- 560 nets, 3200 pins,

- 2 BScan compliant BGA's (total of 688 Pins),

- other high-pin components, total of 956 pins,

- 230 low pin count components;

- total of 5114 Flying Probe test steps,

13 test steps per second ⇒ test time of 6.5 minutes;

- BScan can eliminate 1937 Flying Probe test steps

(38% of all 5114 steps) ⇒ cost saving of \$2.74 per assembly

- 50,000 PCBs per year ⇒ savings potential is \$137.000 annually

# Case Study C

#### Type 3: single PCB, predominantly digital circuits

components with high pin count, many BGA's,

Most components provide Boundary Scan capabilities.

⇒ BScan testing is a "no-brainer"

#### Example:

only alternative: X-ray inspection, however:

- average investment (in-line AXI): \$300,000

- test execution time: AXI >> BScan test;

430mm x 380mm PCB with 50 BGA's:

- Inspection by AXI: 75 seconds

- ~ 10 seconds via BScan

- average costs per test minute calculated as \$1

- production volume of 50,000 PCB's per year,

reduction in test execution time: > \$50,000 savings annually

# Is BScan right for you?

What can BScan potentially do for you?

- Simplify your test

- Lower your cost of test

- Improve your test strategy

Let's find out for sure by doing a Design For Testability analysis

... free of charge [contact info@goepelusa.com]

- + Short test execution

- + Relatively fast test program development

- Expensive test fixtures, maintenance, storage

- New fixtures needed when layout changes

- Typically not available during prototyping

- Test fixtures take weeks to design and build

- Test access limited on modern PCB's

- + No bed-of-nail fixture required

- + Relatively fast test program development

- Very long test execution time

- Modifications of test programs required when layout changes

- Typically not usable in production test

- Test access limited on modern PCB's

- Very good at-speed test to verify UUT functionality

- Very long test development times (cost!)

- Poor diagnostic capabilities

- Difficult fault isolation

- Test of all functions (to cover all faults) practically impossible

- + Short test execution

- + Fast test program development

- Expensive test fixtures, maintenance, storage

- New fixtures needed when layout changes

- Typically not available during prototyping

- Test fixtures take weeks to design and build

- Test access limited on modern PCB's

- + No bed-of-nail fixture required

- + Relatively fast test program development

- + Test of non-electrical properties, such as alignment

- Long test execution time

- No test of electrical properties

- Only visible features can be verified (AOI)

- Very expensive test equipment (AXI)

### **Boundary Scan / JTAG**

- Potential to enhance time to market;

- Available throughout product life cycle;

- Early, easy and fast test development;

- Test for connectivity problems (stuck-at 1/0, open pins, shorted nets);

- Value-adding:

- In-System Programming,

- BIST and Debug access,

- System Test;

# Let ICT vs. Boundary Scan

|                         | In Circuit Test              |                      | Boundary                                 |

|-------------------------|------------------------------|----------------------|------------------------------------------|

|                         | bed of nails                 | Flying Probe         | Scan                                     |

| speed                   | +                            |                      | 0                                        |

| analog devices (power)  | +                            | ++                   | ( <b>—)</b><br>(IEEE 1149.4)             |

| digital devices         | O                            | (-)                  | + (functional description not necessary) |

| net contacting          | —<br>(mechanically)          | —<br>(mechanically)  | +<br>(via test bus)                      |

| flexibility             |                              | +                    | ++                                       |

| costs per new UUT       | <b>– –</b><br>(nail adapter) | O<br>(test creation) | O<br>(test creation)                     |

| costs fortest equipment | _                            | 0                    | ++                                       |

### BScan in Product Life Cycle

### **Boundary Scan / JTAG**

- Regain test access (BGA, CSP, etc.)

- Quick test execution;

- Inexpensive test equipment;

- No or very simple test fixture;

# **Boundary Scan applications**

- Providing test access for ...

- Checking interconnections

- Debugging / emulating circuitry

- Supporting functional test

- Enabling remote test / verification

- Programming devices

•

### Extended Boundary Scan

# Limits of Boundary Scan

- IEEE 1149.1 limited to digital interconnect test

- No at-speed test (exception: BIST)

- New standards (dot4, dot6, ...)

- Combination of Boundary Scan and other Test Methodologies

#### Discussion topics:

What kind of faults do you see most in your production?

When and how to you test?

What is your yield?

What is your slip-through rate?

#### Test Coverage models for structural defects:

- MPS Philips Research (<u>Material</u>, <u>Placement</u>, <u>Solder</u>)

- **PPVS** ASTER Ingénierie (Presence, Polarity, Value, Solder)

- PCOLA/SOQ Agilent Technologies

(<u>Presence, Correctness, Orientation, Live, Alignment, Short, Open, Quality</u>)

#### Of concern for functional test coverage:

- Design defects

- Functional defects

### What is Boundary Scan?

### What is Boundary Scan?

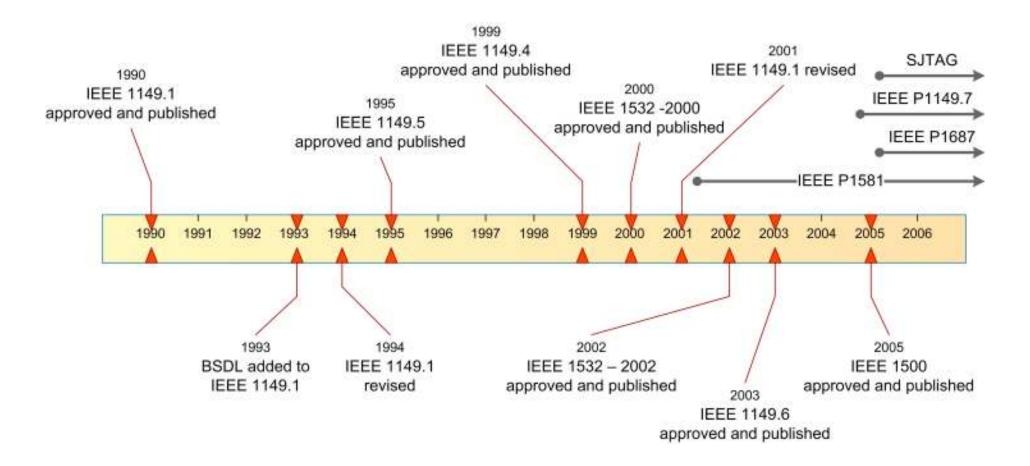

#### A little bit of history (and outlook) ...

#### Component properties:

- Presence

- Correctness (correct device)

- Orientation

- ✓ Live (the device is <u>basically</u> alive)

- Alignment (device is centered, no skews or small rotations)

#### Connections:

- Shorts

- ✓ Opens

- Quality

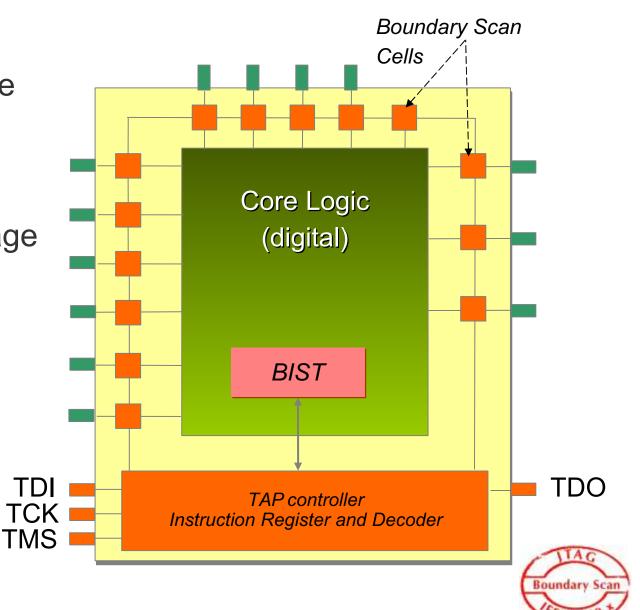

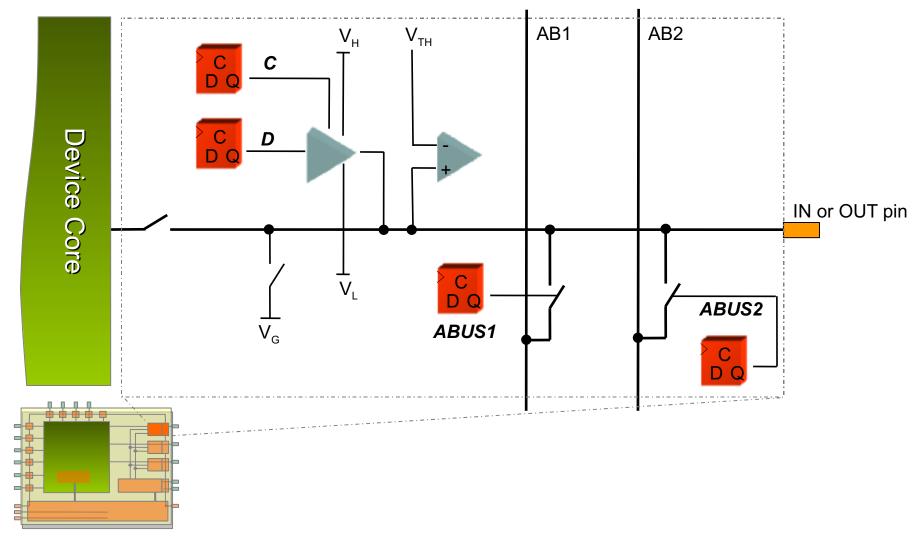

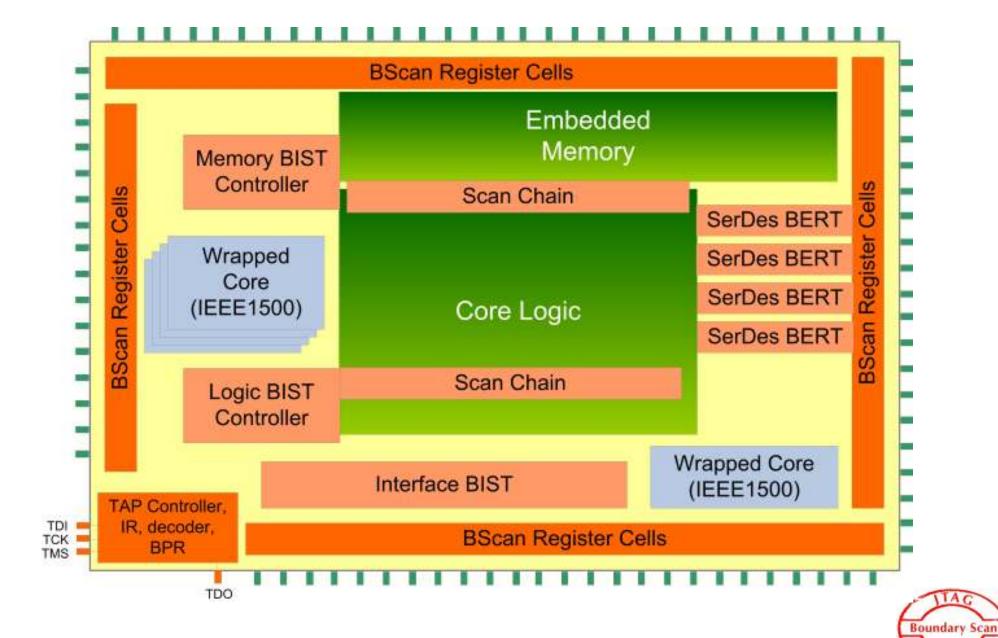

#### Basics of IEEE 1149.1

#### IEEE 1149.1 specifies ...

- Test resources to be implemented in devices

- Boundary Scan

Description Language

(BSDL)

### Basics of IEEE 1149.1

#### **Mandatory** features:

- Test Access Port (TAP):

TCK, TMS, TDI, and TDO

- TAP Controller

- Instruction Register (2 bit or more)

- Bypass Register (1 bit)

- Boundary Scan Register (1 bit or more)

#### Basics of IEEE 1149.1

#### **Optional** features:

- Fifth Test Access Port (TAP) signal: /TRST

- IDCode Register (32 bit)

- UserCode Register (32 bit)

- Other via TAP accessible resources (such as BIST circuitry, in-circuit programming controller, etc.)

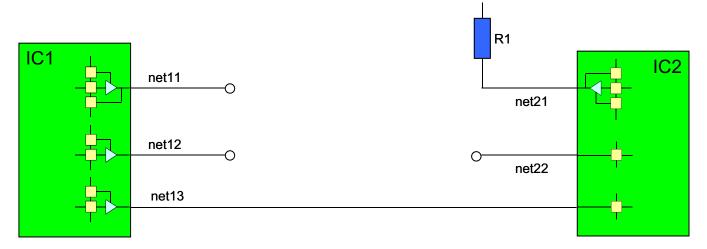

### IEEE 1149.1 in practice

#### Typical applications (only a few examples):

- Check for shorts between BScan accessible nets

- Check for opens on a BScan pin

- Check for stuck-at-0/1 faults at a net level

- Check for missing resistors

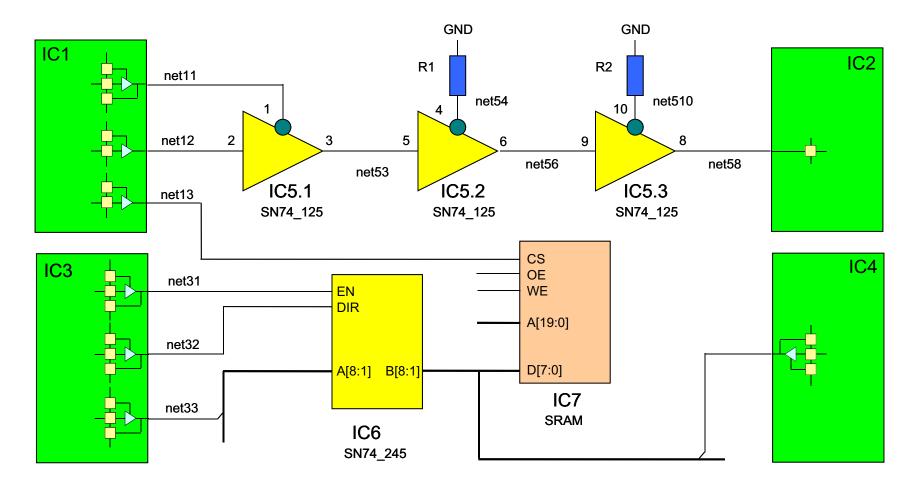

- Check connections to memory devices

- Detect faults in non-BScan circuit clusters

- Control optical indicators (e.g. LED's)

- Provide easy test access for mixed-signal and functional tests

- Use SAMPLE mode to capture signal pattern

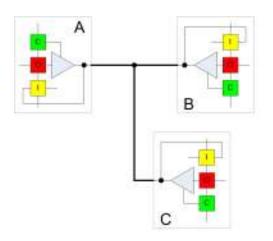

### IEEE 1149.1 in practice

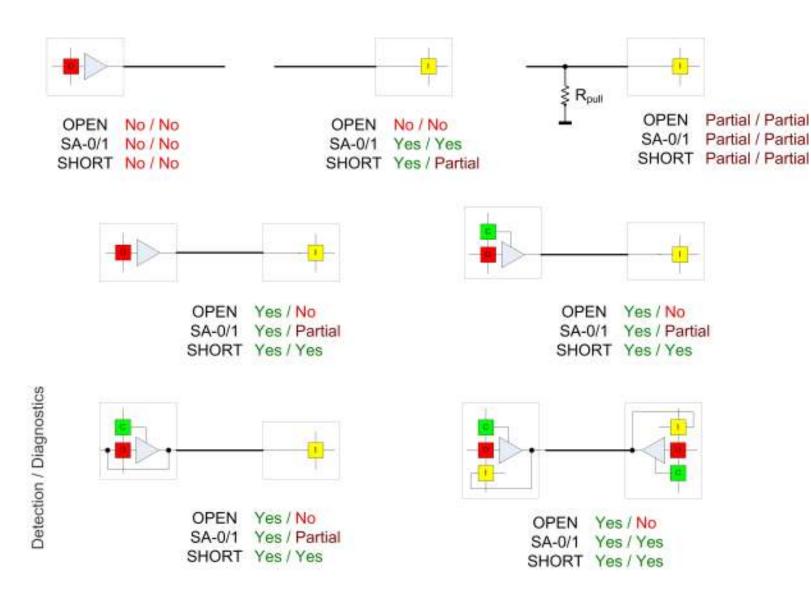

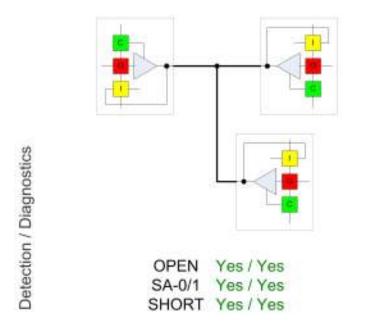

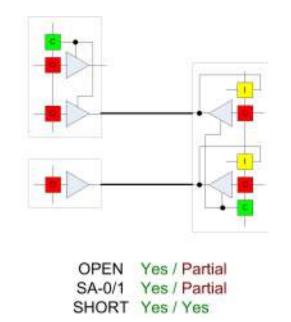

Fault detection, diagnostics depend on BScan resources connected to a particular net:

Fault detection, diagnostics depend on BScan resources

**VDD**

connected to a particular net:

#### Test pattern without and with fault (open pin):

| PASS                      | Α |   |   | В |   |   | C |   |   |

|---------------------------|---|---|---|---|---|---|---|---|---|

|                           | C | 0 | 1 | C | 0 | 1 | C | 0 | П |

| Preload pattern           | L | Z | Н | L | Z | Н | L | Z | Н |

| A drives, B and C measure | H | L | L | L | Z | L | L | Z | L |

| A drives, B and C measure | Н | Н | Н | L | Z | Н | L | Z | Н |

| B drives, A and C measure | L | Z | L | H | L | L | L | Z | L |

| B drives, A and C measure | L | Z | Н | Н | Н | Н | L | Z | Н |

| C drives, A and B measure | L | Z | L | L | Z | L | Н | L | L |

| C drives, A and B measure | L | Z | Н | L | Z | Н | Н | Н | Н |

| FAIL                      | Α |   |   | В |   |    | C |   |   |

|---------------------------|---|---|---|---|---|----|---|---|---|

|                           | C | 0 | 1 | C | 0 | 18 | C | 0 | 1 |

| Preload pattern           | L | Z | Н | L | Z | Н  | L | Z | H |

| A drives, B and C measure | Н | L | L | L | Z | H  | L | Z | L |

| A drives, B and C measure | Н | Н | Н | L | Z | Н  | L | Z | H |

| B drives, A and C measure | L | Z | H | H | L | L  | L | Z | H |

| B drives, A and C measure | L | Z | Н | Н | Н | Н  | L | Z | H |

| C drives, A and B measure | L | Z | L | L | Z | H  | Н | L | L |

| C drives, A and B measure | L | Z | Н | L | Z | Н  | Н | Н | Н |

#### How about non-BScan devices?

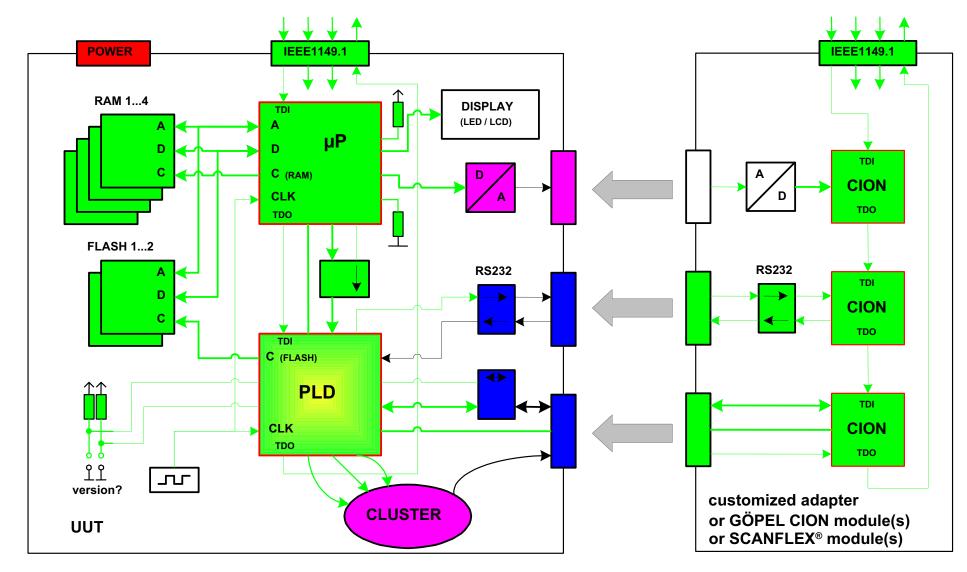

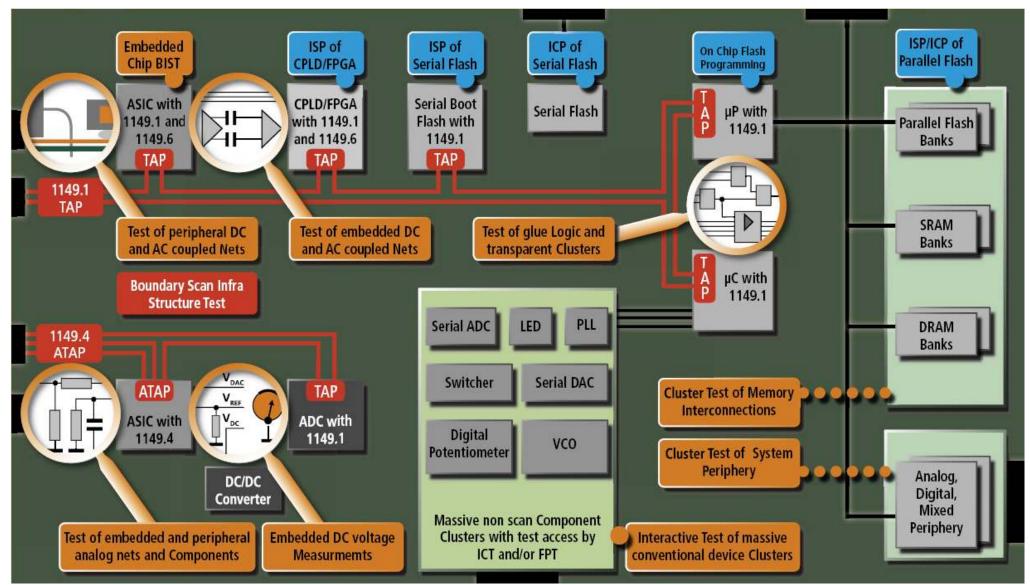

## **Board Level applications**

ISP = In-System Programming

ICP = In-Circuit Programming

BIST = Built-In Self Test

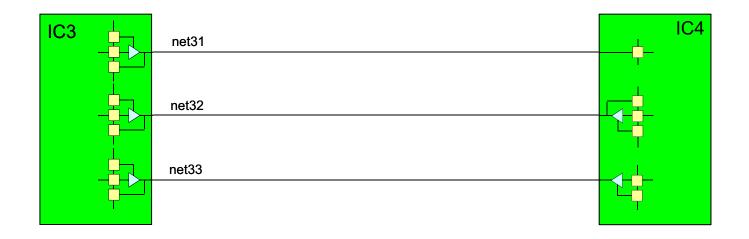

### **Board Level applications**

- Infrastructure Test

- Interconnection Test

- Memory Cluster Test

- Logic Cluster Test

- Other Cluster Tests

- ISP for FLASH

- ISP for serial EEPROM

- ISP for PLD/FPGA

- BIST

- Emulation, Debugging, Fault Insertion, ...

### **BScan / Functional Test**

- Low cost, flexible, powerful

- Very good test coverage, diagnostics:

- Boundary Scan for structural test

- Functional Test for parametric and at-speed test

- BScan for simplified access in functional tests

- Integrated, highly automated test flow

- Combination through API's; off-the-shelf or ad-hoc software

- Parametric Test for

- Passive components (resistors, capacitors, inductors, etc.) and/or passive elements intrinsic to the interconnect

- Pull- or termination resistors

- Active components (diodes, transistors, sensors, etc.)

- Impedance networks

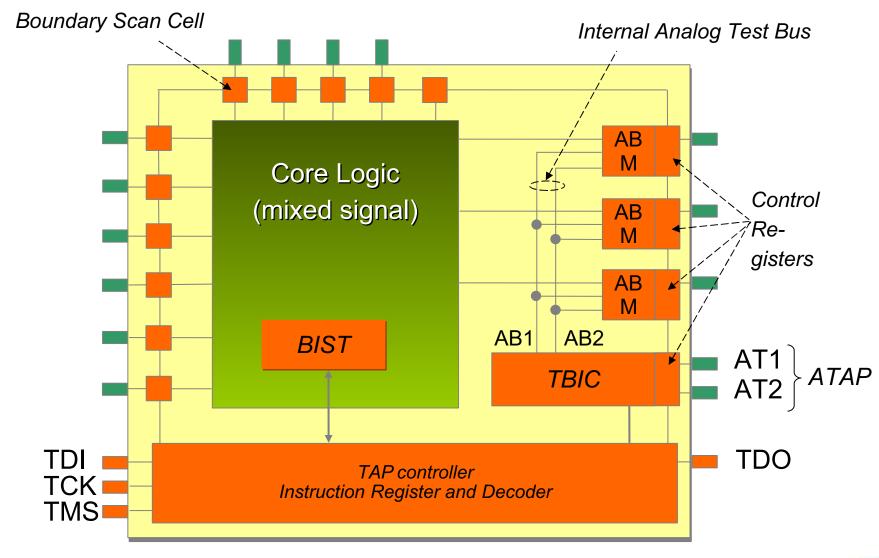

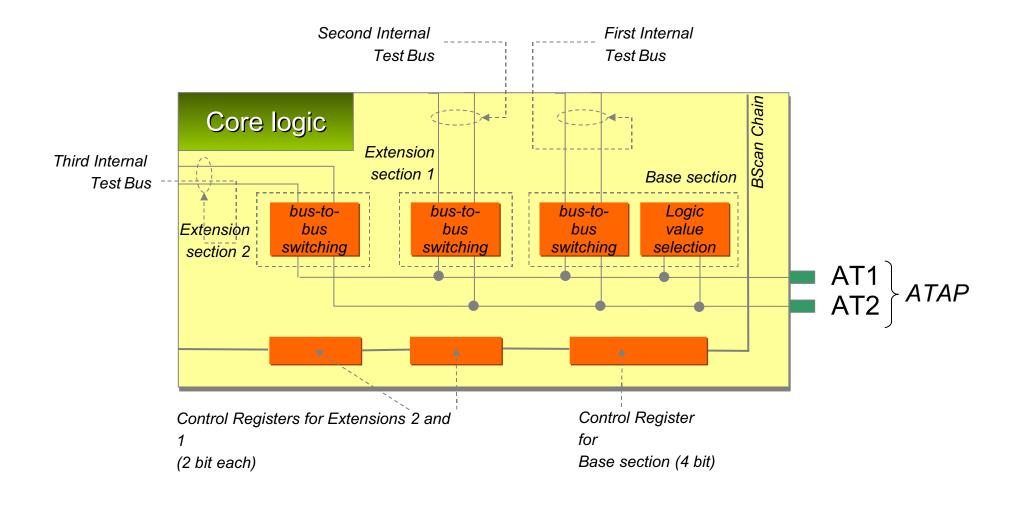

- Extended Interconnect Test

- Limited number of devices available

- Emerging tool support

- Extending Interconnect Test to AC-coupled networks

- Standard approved in 2003

- Devices are emerging

- Tool support is available

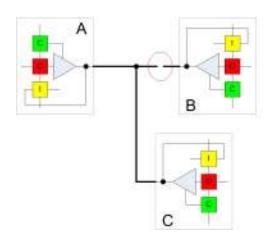

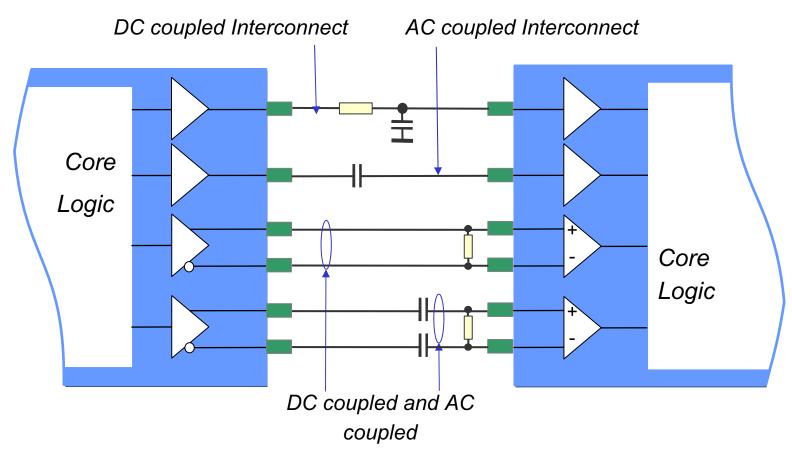

# Purpose of IEEE 1149.6

- Extending IEEE-Std. 1149.1 capabilities by providing test methodology for

- Differential interconnections

- AC coupled networks

- Defines hardware structure and two new instructions

# Principle of IEEE 1149.6

- Operates in parallel with 1149.1 and 1149.4

- Proposes a way of testing AC coupled networks by providing AC Test Signal on output and recovering signal on inputs

- Access to test resources through IEEE-1149.1 TAP

# Signal coupling

differential Interconnects

Shown above are just a few sample coupling schemes Coupling capacities could also be implemented inside the IC

# 1149.6 Main Features

- A IEEE-1149.6 compliant device is also 1149.1 compliant

- New AC-Test instructions defined in 1149.6:

- EXTEST\_PULSE (mandatory)

- EXTEST\_TRAIN (mandatory)

- AC-pins receiving data have test receiver:

- Single ended AC-pin: one test receiver

- Differential channel: two test receiver

- AC outputs use mission driver

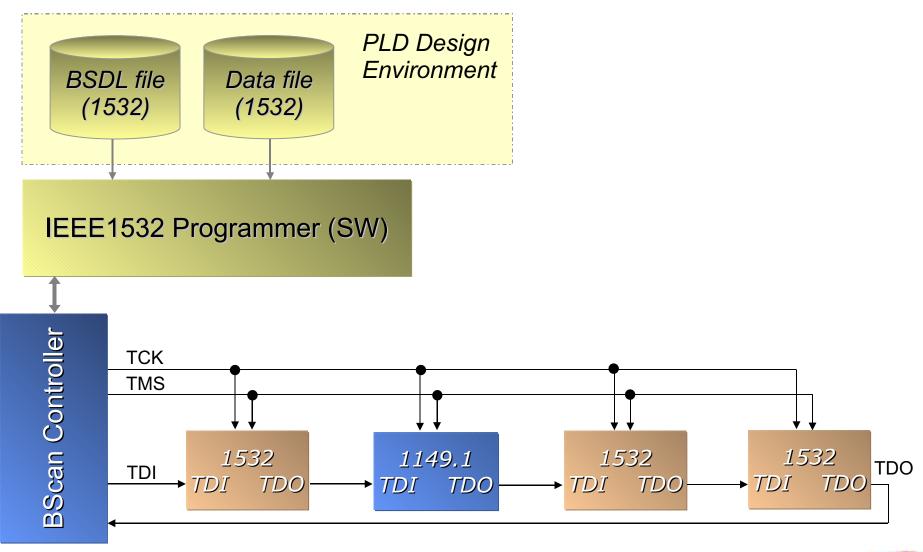

### **Basics of IEEE 1532**

- Standardized in-system programming (ISP) method

- Formal extension to IEEE-1149.1b-1994

- Access to on-chip programming resources via TAP

- Unified programming approach for devices from different vendors

- Concurrent programming of multiple devices from different vendors, reducing cost related to ISP

- Data and programming algorithm in separate files

#### **Basics of IEEE 1532**

# New standards / initiatives

- IEEE P1581

- IEEE P1149.7 (cJTAG)

- SJTAG

- IEEE P1687 (IJTAG)

- other

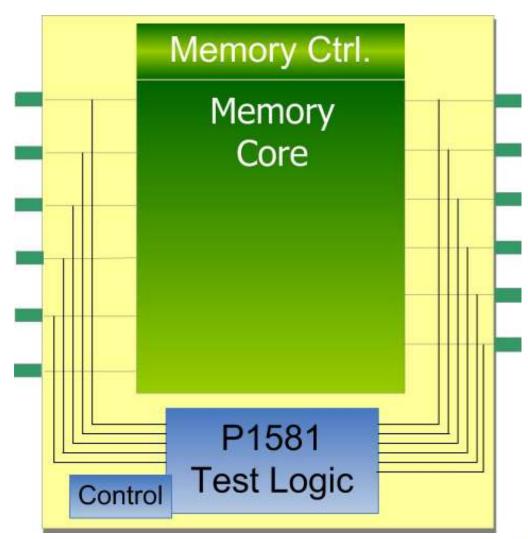

### **Basics of IEEE P1581**

- To test connectivity to non-BScan devices easily

- Solve test problems for devices such as DDR-SDRAM, DDR2-SDRAM, FLASH, etc.

- → 1149.1 not built in!

- Controllability, complexity

- Test time

- Test conditions (use of untested resources to test the DUT)

- Simple, quasi-static interconnect test (no need for at-speed access or initialization)

- Multiple P1581 devices in bus structure

### **Basics of IEEE P1581**

# Device is a "slave"

#### **Test Control:**

Optional Test Pin

#### Or

Test Control Circuitry (various proposals)

# P1581 test logic circuitry

- XOR/XNOR, or Inverters/AND

- Only combinational, non-sequential logic

- Easy to implement, simple test vectors

- Faults on pins don't inhibit test of other pins

- Fault detection guaranteed

- Fault diagnostics depends on implementation, test vectors

- Patented vs. public domain

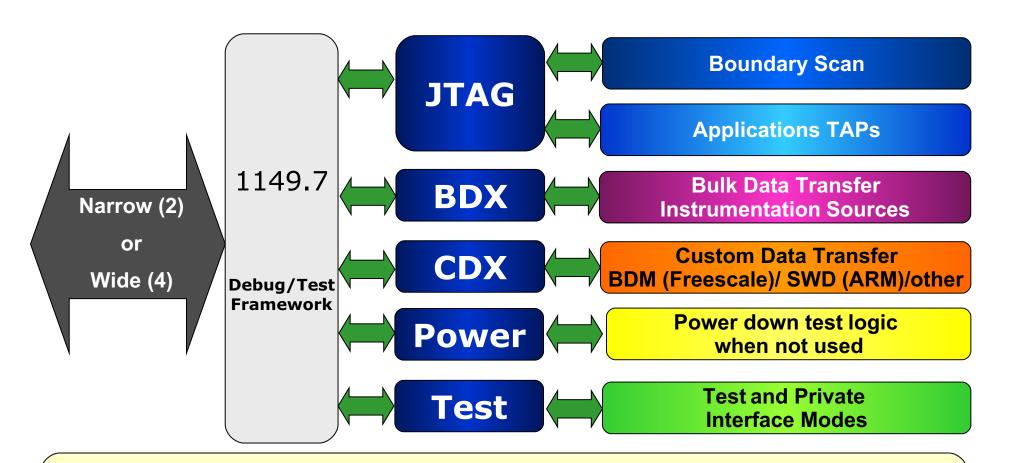

- ◆ IEEE 1149.1 signaling used at start-up

- SW directed mode switches between JTAG modes and advanced modes

- SW directed mode switches between JTAG modes and advanced modes. Software drivers always use IEEE state sequences.

- **♦** Framework for multiple debug and other technologies

### **Basics of IEEE P1687**

#### Focus on

- Documentation: architectural descriptions

- Identify accessible embedded instruments,

- Specify characteristics of the instrument;

- Access protocols: procedure descriptions

- How to communicate with an instrument,

- Facilitate re-use through portability;

- "Enhanced", secondary access/interface:

- Access instruments not easily handled solely by the TAP (i.e. use high bandwidth I/O)

- Simplify hierarchical test architectures

### Basics of IEEE P1687

#### Goal:

to standardize data contents and formats for communication:

between external Test Manager platforms and internal Embedded Test Controllers,

#### and

between Embedded Test Controllers and the UUTs they serve

for all variants of XBST and EBST

XBST - external Boundary Scan Test EBST - embedded Boundary Scan Test

#### Books:

- Boundary Scan Handbook, 3<sup>rd</sup> Edition, Ken P. Parker, Kluwer Academic Publishers, ISBN 1-4020-7496-4

- Analog and Mixed-Signal Boundary-Scan, Adam Osseiran, Kluwer Academic Publishers, ISBN 0-7923-8686-8

- Digital Systems Testing and Testable Design, Miron Abramovici et.al., IEEE Press, Wiley Interscience, ISBN 0-7803-1093-4

#### Websites:

- www.goepelusa.com

- www.freeDFT.info

- www.DFTdigest.com

#### Other publications:

- ITC Proceedings (papers on the topic; there are plenty ...)

- Testability Guidelines, SMTA TP-101C (2002), www.smta.org

#### For further information, please:

- Visit our website at www.goepelusa.com

- Contact your local sales representative

- Call us at 1-888-4GOEPEL

- Email us at sales@goepelusa.com