# **Evolution of Digital Verification**

Walter Gude Applications Engineering Consultant Walter\_gude@mentor.com

Presented to the IEEE Long Island Section Signal Processing Society & Photonics Society on Tuesday October 8th, 2013

## Agenda

#### Verification Overview

- Assertion and Functional Coverage

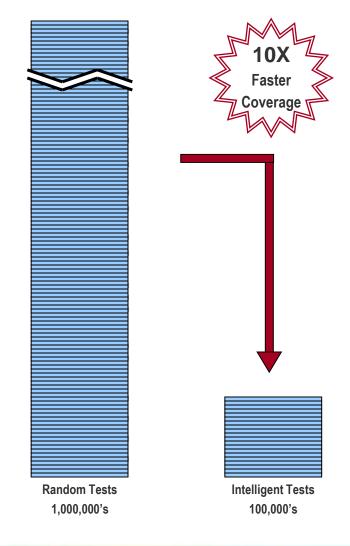

- Constrained Random

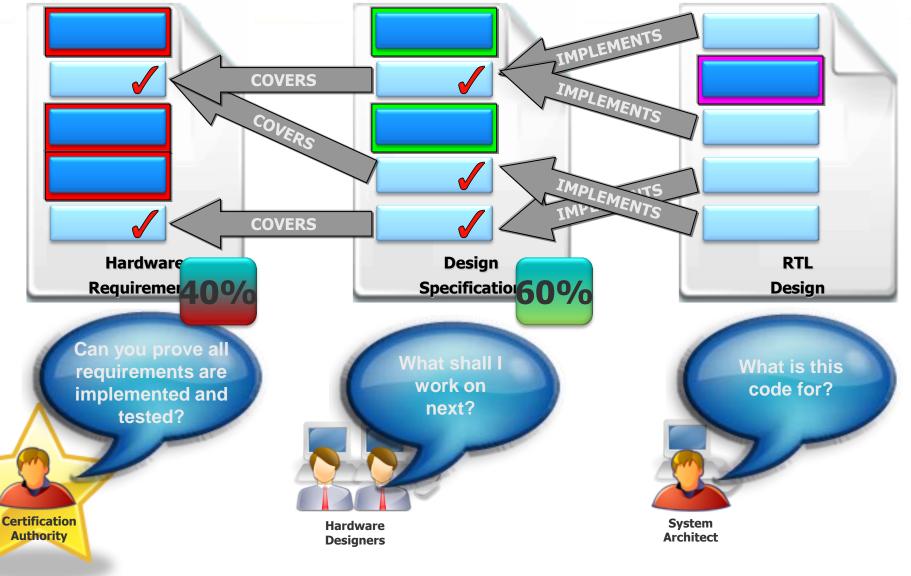

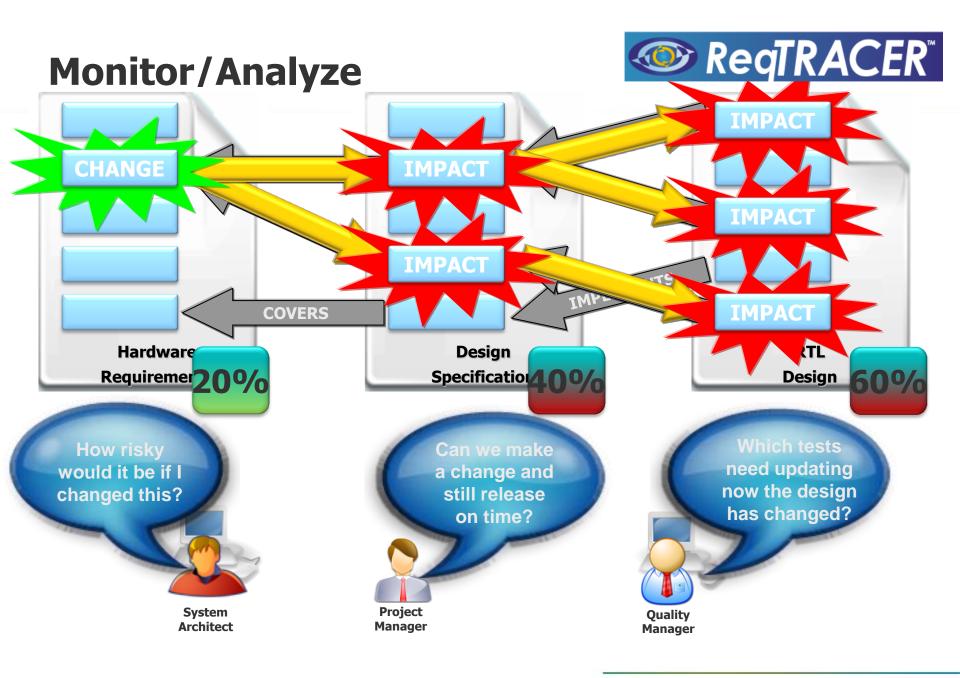

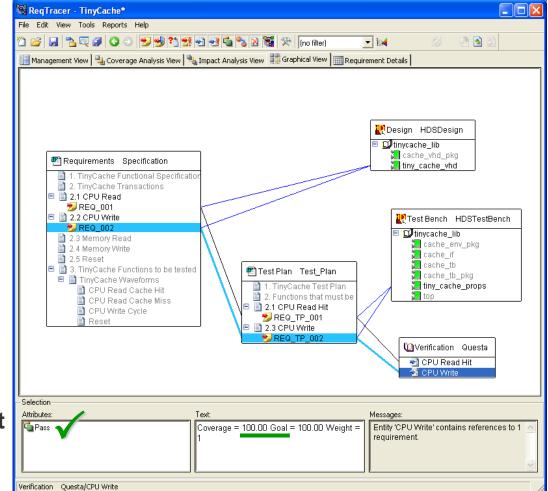

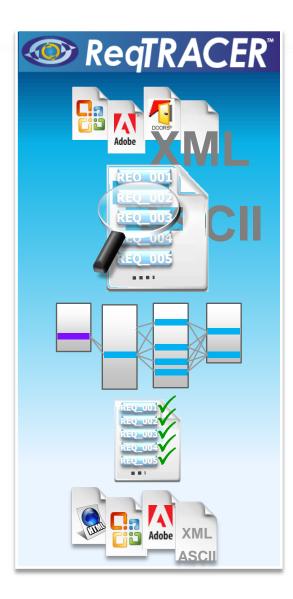

- Requirements Tracing

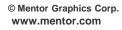

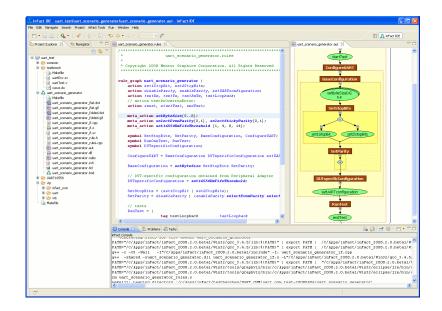

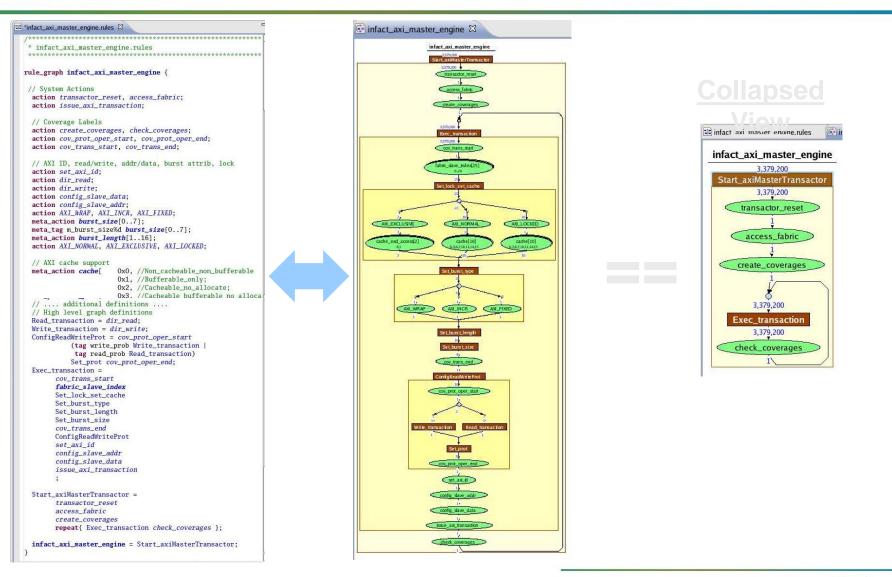

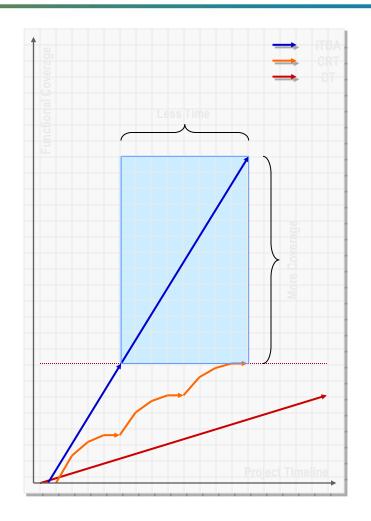

- Algorithmic TB InFact

- Questa Formal

- Questa Codelink

- Questa VIP

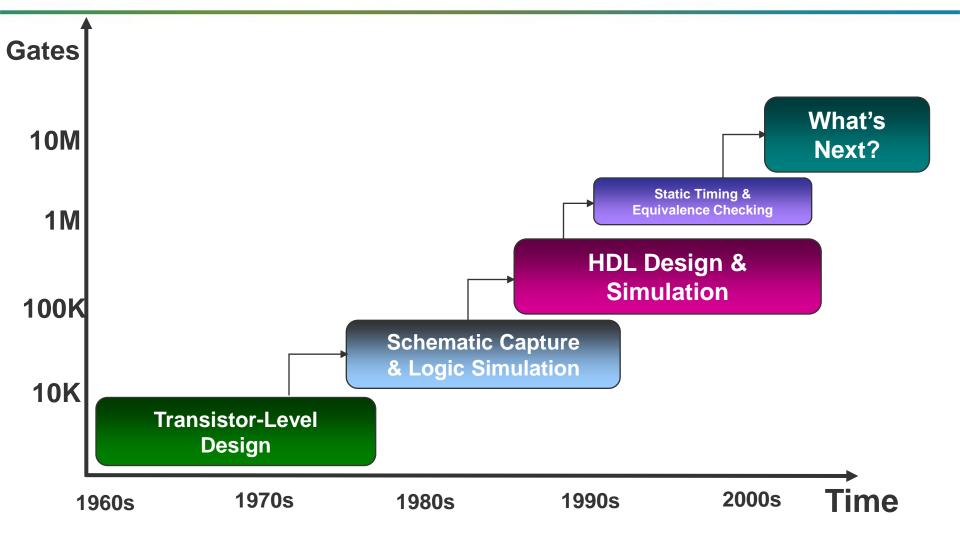

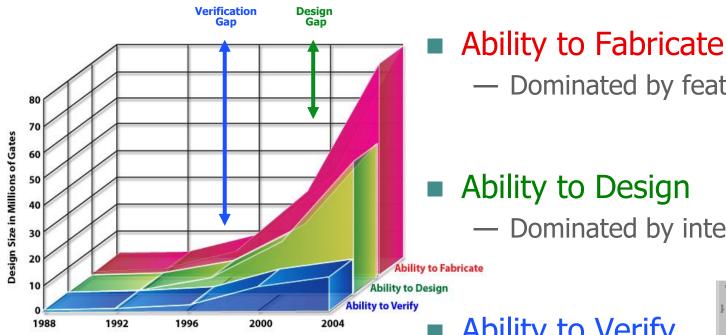

## **The Evolution of Digital Design & Verification**

#### Creating HUGE Verification Challenges

Dominated by feature size

Ability to Design

Dominated by interconnect

Ability to Verify

Dominated by behavior over time and complexity of concurrency

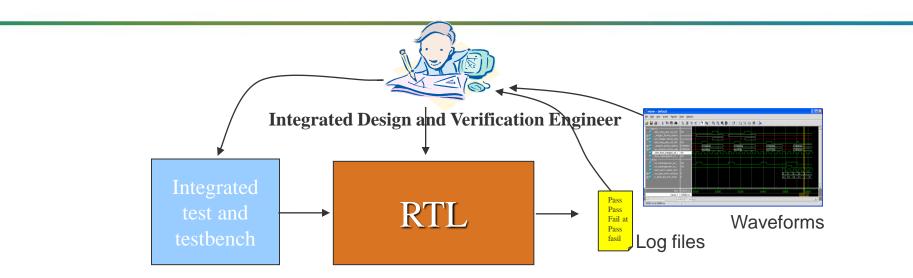

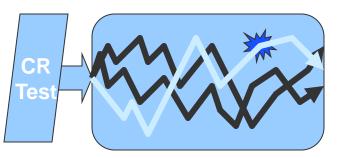

#### **Traditional Directed Test Flow....**

- Mainly directed tests

HDL and some C/C++

- Ad hoc test planning

- Code Coverage tools for advanced users

- Manually inspected output files and waveforms

- Problem: Creation of directed tests does NOT scale with increased complexity

- Number of tests directly linked to number of engineers writing tests

- Amount of testbench code becomes difficult to manage

- NEED better way to create stimulus!

- Problem: Code Coverage does not measure how well specifications are covered.

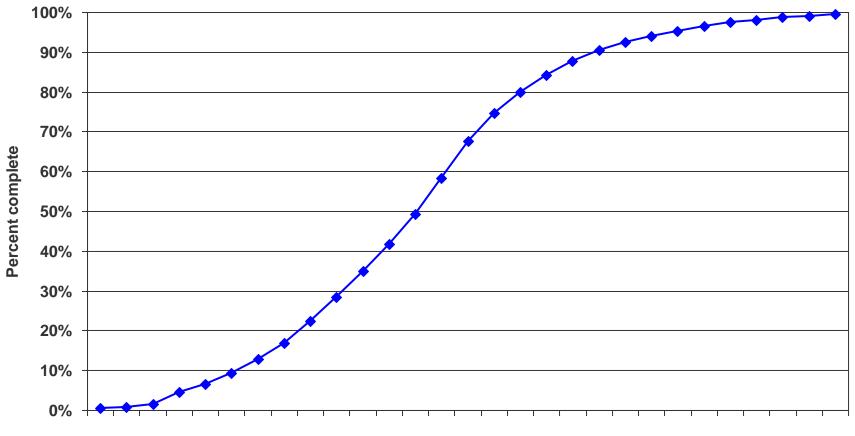

#### **When Is Verification Complete?**

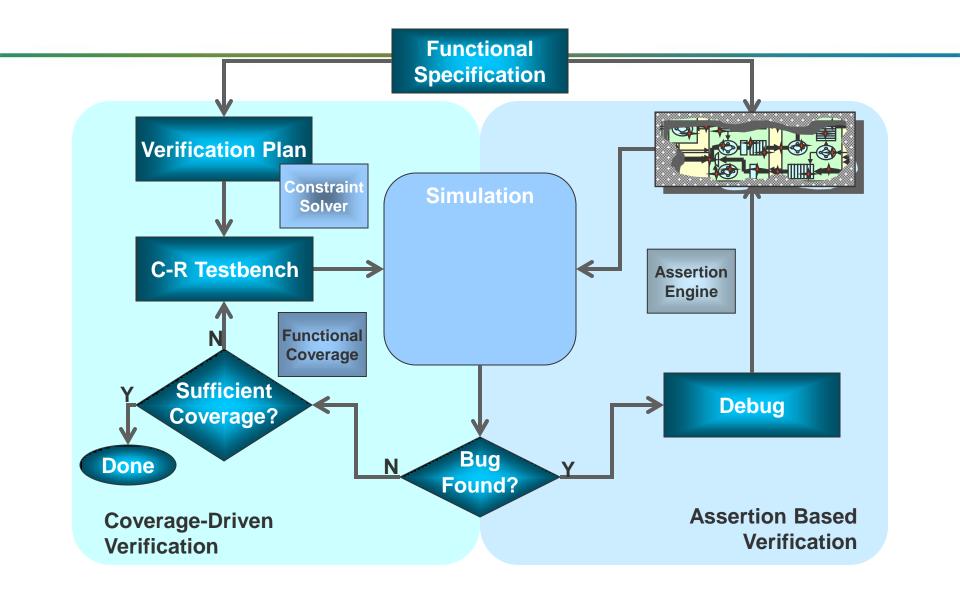

#### **Advanced Verification**

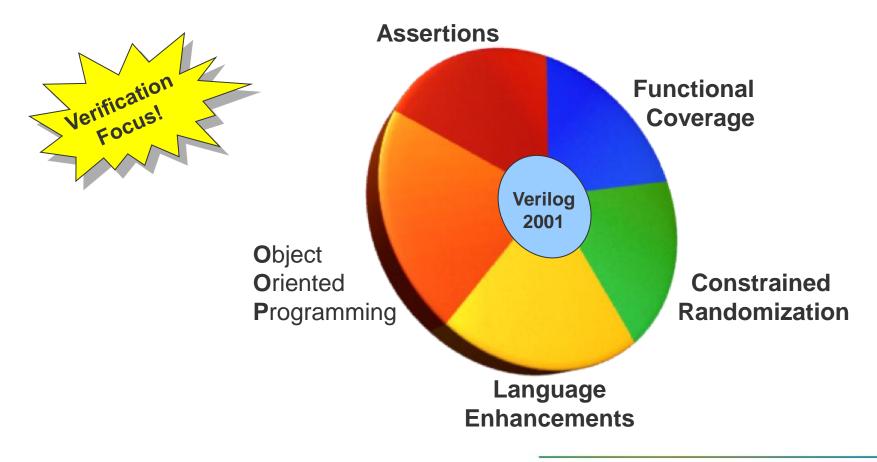

### **SystemVerilog**

- Verilog 2001 base...

- Massive enhancements

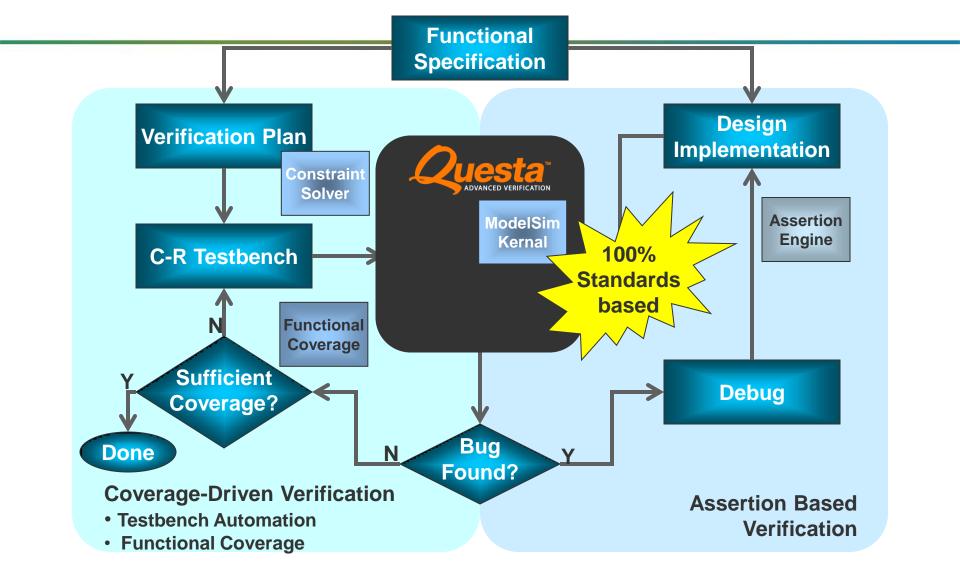

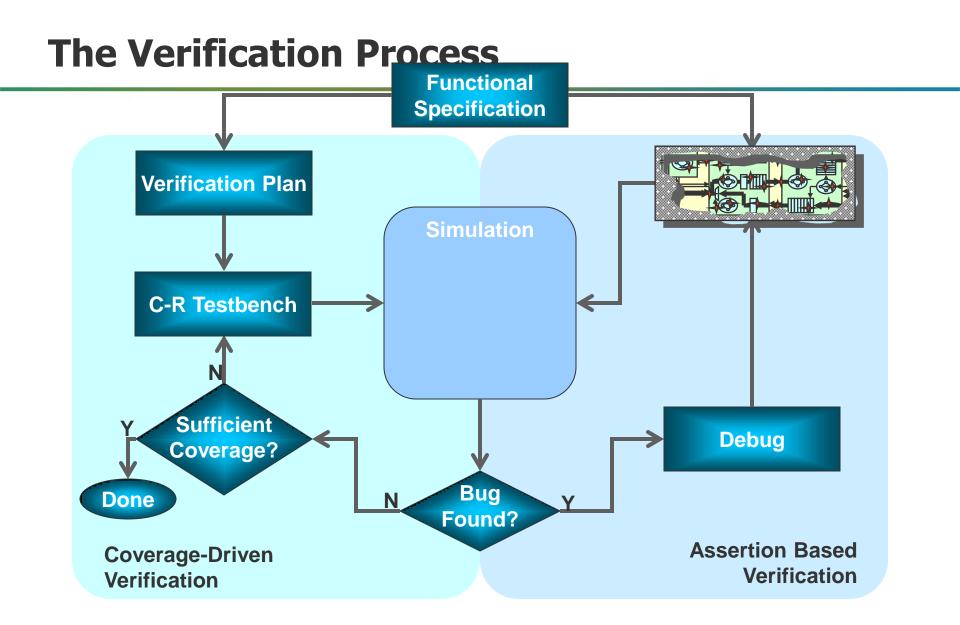

## **The Verification Process**

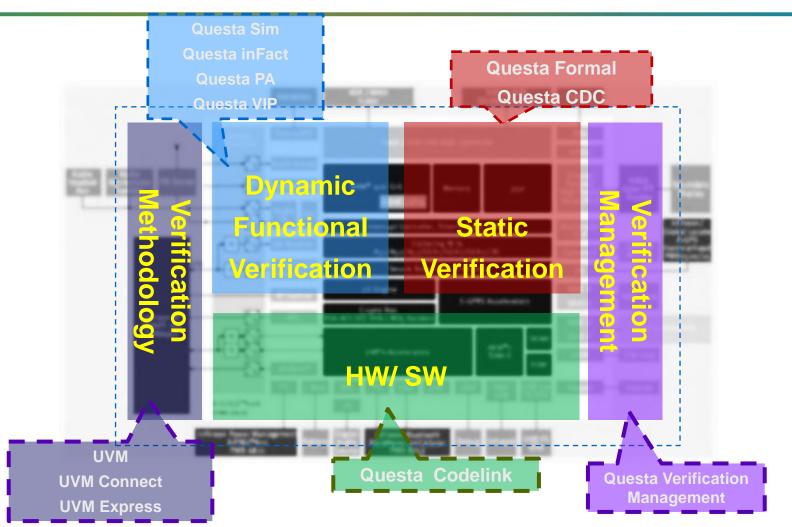

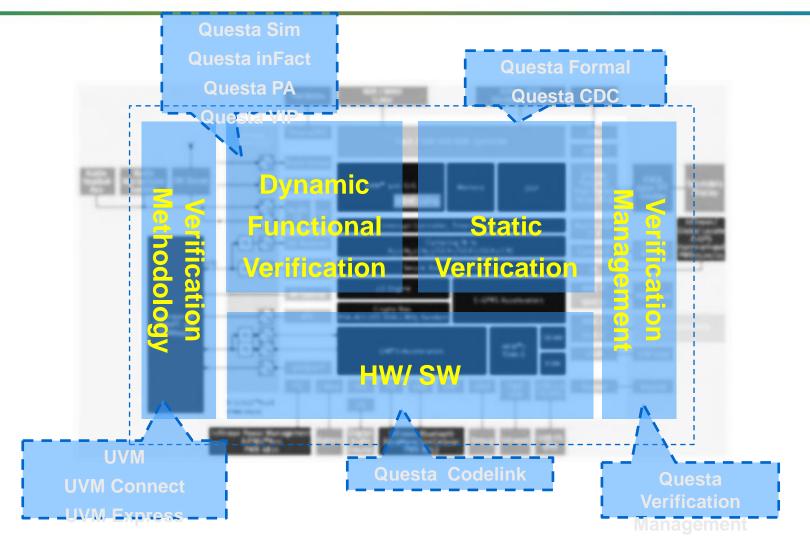

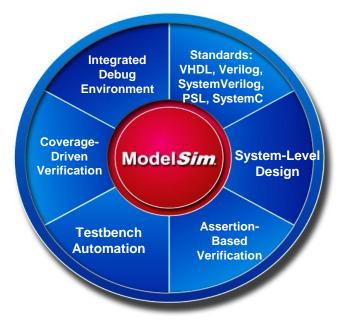

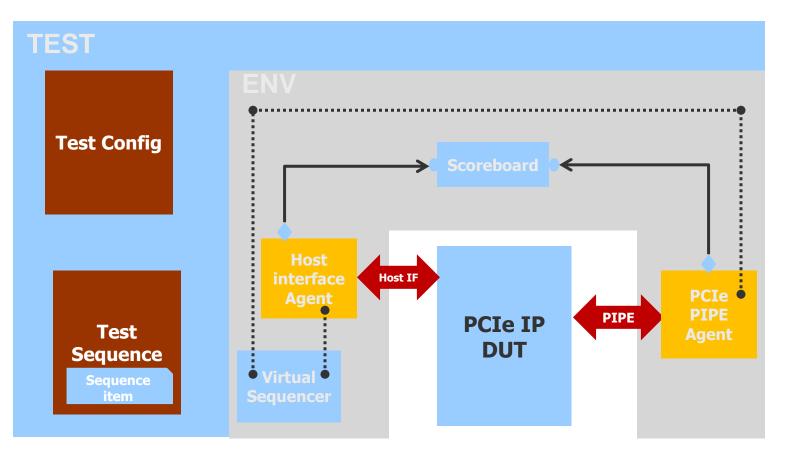

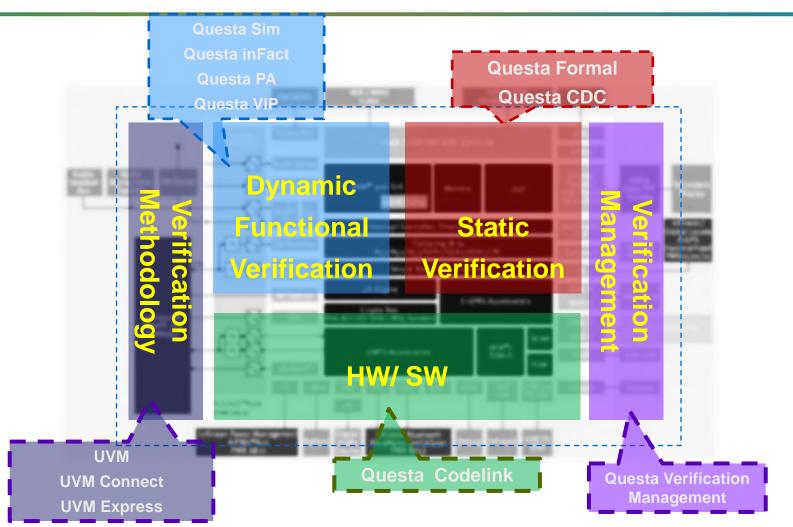

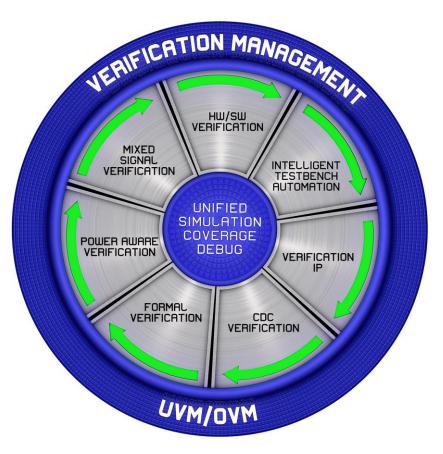

## **Questa Verification Platform**

Best In Class Engines

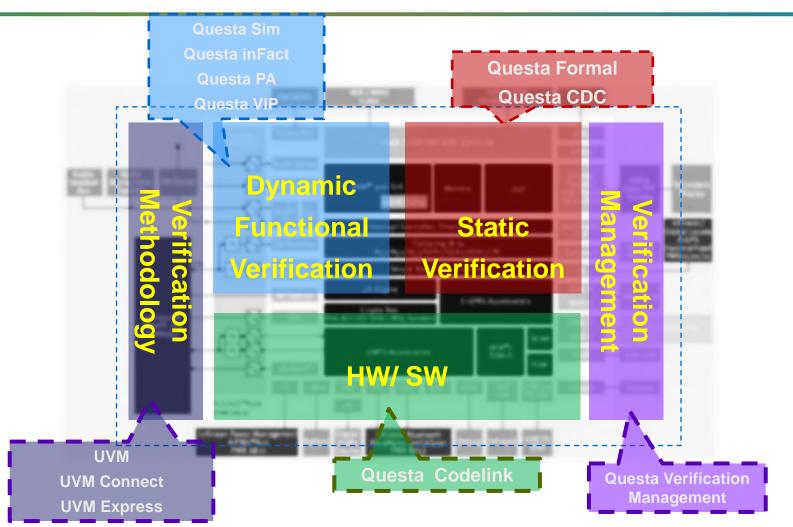

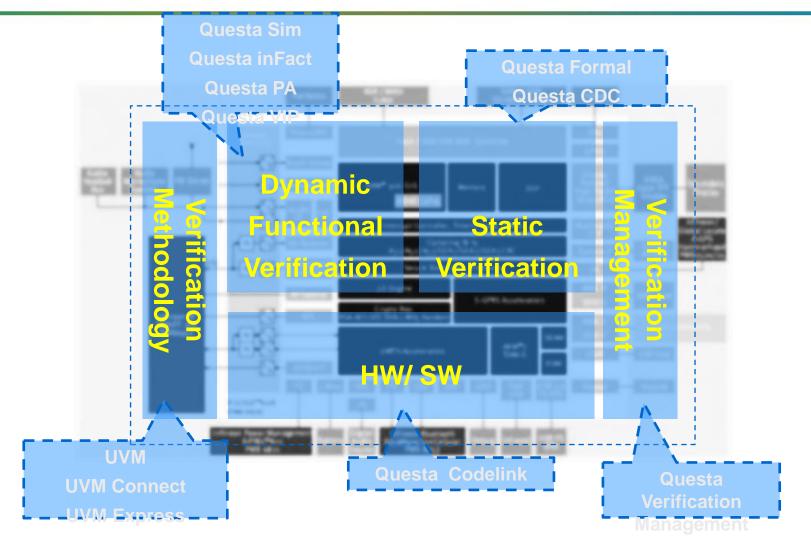

## **Questa Verification Platform**

Best In Class Engines - Unified Front End Analysis & Compile

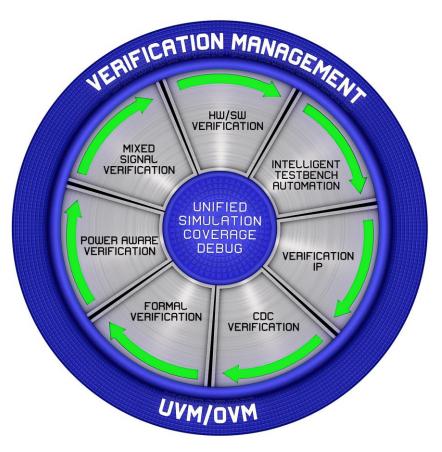

## **Questa Verification Platform**

- Comprehensive integrated SOC verification platform

- Best in class engines

- Integrated

- Comprehensive debug analysis

- Industry Leading SOC Verification Solutions

- Coverage Closure Solution

- Low Power Verification Solution

- Software Driven Verification Solution

- Standards Leadership

- Driving the evolution of IEEE standards

- Major donations to Accellera UVM

- Accellera UCIS from Mentor UCDB

#### What is an Assertion?

A concise description of [un]desired behavior

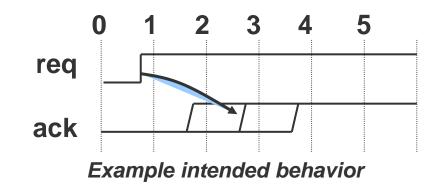

"After the request signal is asserted, the acknowledge signal must come 1 to 3 cycles later"

#### SV Assertions SV Assertion property req ack(req,ack); @(posedge clk) \$rose(req) |-> ##[1:3] \$rose(ack); endproperty as req ack: assert property (req ack(req1,ack1)); sample inputs : process (clk) VHDL begin if rising edge(clk) then STROBE REQ <= REQ; STROBE ACK <= ACK; end if; 2 3 0 end process; protocol: process variable CYCLE CNT : Natural; req begin loop wait until rising edge(CLK); exit when (STROBE REQ = '0') and (REQ = '1'); ack end loop; CYCLE CNT := 0;Example intended behavior loop wait until rising edge(CLK); CYCLE CNT := CYCLE CNT + 1; exit when ((STROBE ACK = '0') and (ACK = '1')) or (CYCLE CNT = 3); end loop; if ((STROBE ACK = '0') and (ACK = '1')) then report "Assertion success" severity Note; else report "Assertion failure" severity Error; end if; HDL Assertion end process protocol;

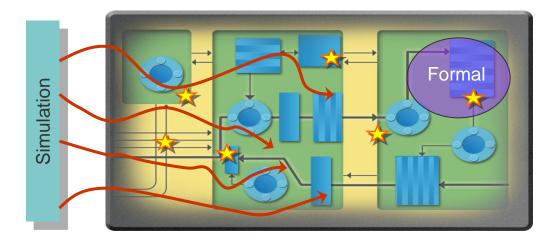

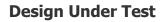

# **Assertions Need to be Everywhere**

Assertions Enable Higher Quality Designs

- Assertions provide observability for higher complexity designs

- Assertions describe (un)desired behavior

- Assertions dramatically shorten debug and repair time

- Bus Monitor Assertion Reckers Bus Monitor Assertion Checkers Bus Monitor Assertion Checkers

- Assertions stay on during block, chip and system-level tests

- Finds bugs you weren't looking for

## **Payoff Is High: Assertions Find Bugs**

|                              | 0.40/ |

|------------------------------|-------|

| Assertion Monitors           | 34%   |

| Cache Coherency Checkers     | 9%    |

| Register File Trace Compares | 8%    |

| Memory State Compare         | 7%    |

| End-of-Run State Compare     | 6%    |

| PC Trace Compare             | 4%    |

| Self-Checking Test           | 11%   |

| Simulation Output Inspection | 7%    |

| Simulation Hang              | 6%    |

| Other                        | 8%    |

|                              |       |

Kantrowitz and Noack [DAC 1996]

| Pagister Missompares     |            |

|--------------------------|------------|

| Register Miscompares     | <u>22%</u> |

| Simulation "No Progress" | 15%        |

| PC Miscompare            | 14%        |

| Memory State Miscompare  | 8%         |

| Manual Inspection        | 6%         |

| Self Checking Test       | 5%         |

| Cache Coherency Check    | 3%         |

| SAVES Check              | 2%         |

34% of all bugs found were identified by assertions on DEC Alpha 21164 project

[Kantrowitz and Noack DAC 1996]

17% of all bugs found were identified by assertions on Cyrix M3(p1) Project

[Kronik '98]

25% of all bugs found were identified by assertions on DEC Alpha 21264 project

[Taylor et al. DAC 1998]

50% of all bugs were identified by assertions on Cyrix M3(p2) Project

[Kronik '98]

85% of all bugs were found using over 4000 assertions on HP Project

[Foster and Coelno HDLCon 2000]

10,000 assertions in Cisco project

[Sean Smith 2002]

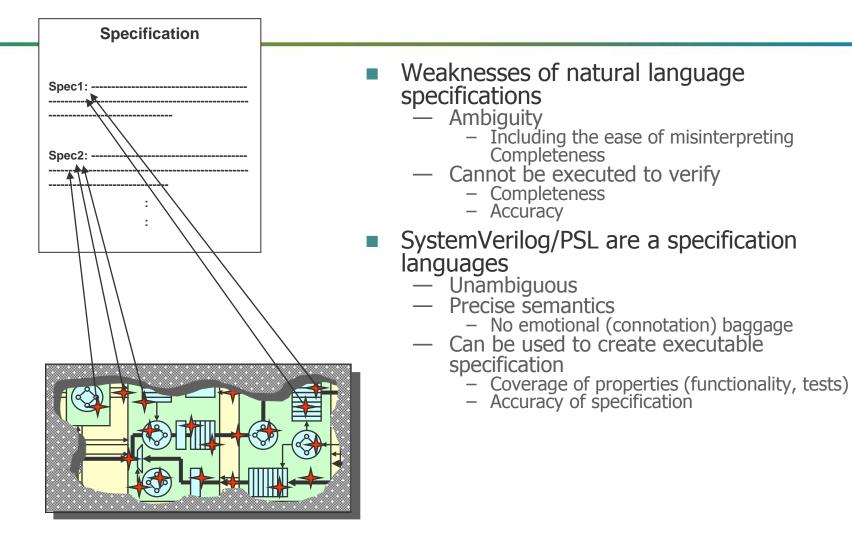

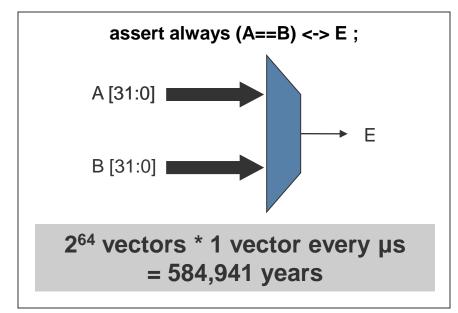

# **Formal Specification**

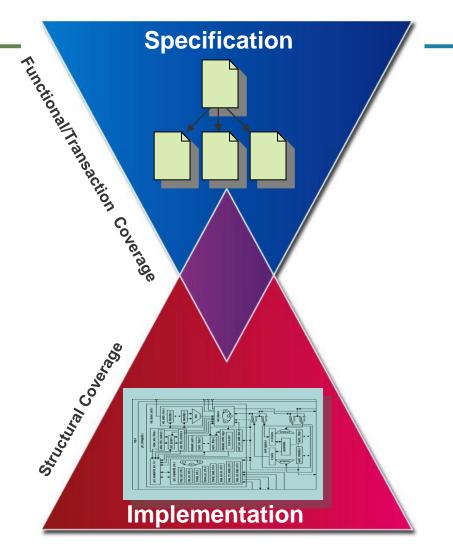

## **Total Coverage Model**

- Functional (specification-based)

- Checks that all functions of the design are tested

- Created by verification team

- Structural (implementation-based)

- Checks that all corner-cases of the design are tested

- Created by designers

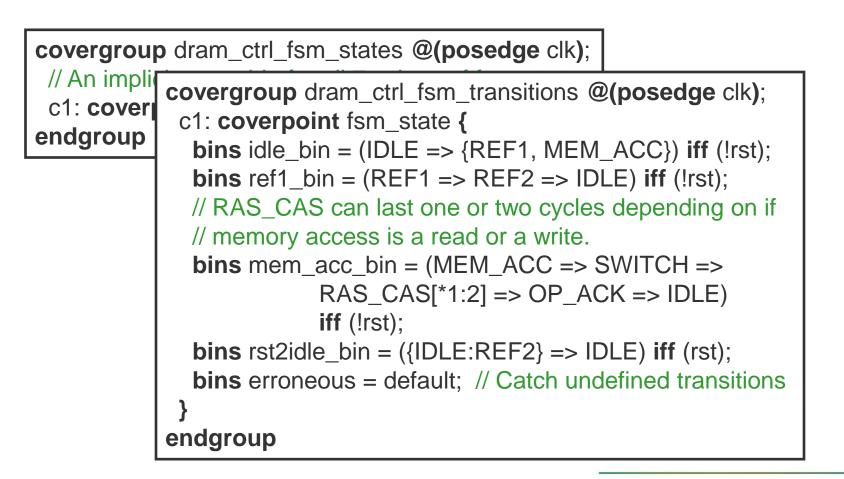

#### **SV Coverage Models**

// States for a DRAM controller

enum {IDLE, MEM\_ACC, SWITCH, RAS\_CAS, OP\_ACK, REF1, REF2} fsm\_state;

## When is verification complete?

- Verification is effectively metric-less

- Few designers know if their strategy is adequate or efficient

- Sign-off criteria are ad hoc and vary by company

- Code coverage is not a functional verification metric

- If it isn't verified, it's broken

## **When Is Verification Complete?**

|   | 100% -       | 1 | M Funct         | ional coverage    | s        |              |       |         |       |            |             | X        |

|---|--------------|---|-----------------|-------------------|----------|--------------|-------|---------|-------|------------|-------------|----------|

|   |              |   | Functional      | coverages 💳       |          |              |       |         |       |            |             | ∉ ×      |

|   | 90% -        |   | ▼Name           |                   | Design U | nit Enabled  | Count | AtLeast | Weigh | nt Cmplt % | Cmplt graph | <b>•</b> |

|   | <b>JU</b> /0 |   | ⊟– <b>,</b> eth | _cop              | Verilog  |              |       |         |       | 0%         |             |          |

|   |              |   | ₫→              | /top/i_eth_cop/c  | .psl     |              | 0     | 1       |       | 1 0%       |             |          |

|   | 80% -        |   | ₫-▲             | /top/i_eth_cop/c  | .psl     | ×            | 0     | 1       |       | 1 0%       |             |          |

|   |              |   | ∲-→             | /top/i_eth_cop/c  | .psl     | ×            | 0     | 1       |       | 1 0%       |             |          |

|   | 700/         |   | <u> </u>        | /top/i_eth_cop/c  | .psl     | XX           | 0     | 1       |       | 1 0%       |             |          |

|   | <b>70%</b> - |   | ⊟- <b>⊒</b> eth | _rxstatem         | Verilog  |              |       |         |       | 0%         |             |          |

| 1 |              |   |                 | /top/ethtop/rxeth |          |              | 0     | 1       |       | 1 0%       |             |          |

|   | 60%          |   |                 | /top/ethtop/rxeth |          | ×            | 0     | 1       |       | 1 0%       |             |          |

|   | 00 /0        |   |                 | /top/ethtop/rxeth | .psl     | ×            | 0     | 1       |       | 1 0%       |             |          |

|   |              |   | ⊡- <b>⊒</b> eth |                   | Verilog  |              |       |         |       | 95%        |             |          |

|   | <b>50%</b> · |   |                 | /top/ethtop/cov   |          |              | 26    | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   | psl      | <b>√</b>     | 6     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | C /top/ethtop/    |          |              |       |         |       |            |             |          |

|   | <b>40%</b>   |   |                 | S /top/ethtop/s   |          |              |       |         |       |            |             |          |

|   |              |   |                 |                   |          |              |       |         |       |            |             |          |

|   | 200/         |   |                 | L_ /top/etht      |          |              |       |         |       |            |             |          |

|   | <b>30%</b> · |   |                 | /top/ethtop/cov   |          | •            | 9     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   |          | •            | 11    | 1       |       | 1 100%     |             |          |

|   | 20% -        |   |                 | /top/ethtop/cov   |          | <b>√</b>     | 9     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   |          | $\checkmark$ | 2     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   |          | $\checkmark$ | 3     | 1       |       | 1 100%     |             |          |

|   | 10% -        |   |                 | /top/ethtop/cov   |          | ×.           | 4     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   |          | ×.           | 10    | 1       |       | 1 100%     |             |          |

|   | •••          |   |                 | /top/ethtop/cov   |          | ×.           | 5     | 1       |       | 1 100%     |             |          |

|   | 0% -         |   |                 | /top/ethtop/cov   |          | ×            | 5     | 1       |       | 1 100%     |             |          |

|   |              |   |                 | /top/ethtop/cov   |          | 1            | 0     | 1       |       | 1 0%       |             |          |

|   |              |   | 🗄 🖊             | /top/ethtop/cov   | psi      | <u>√</u>     | 4     |         |       | 1 100%     |             | -        |

# **Directed Tests**

# Functional Coverage and Contrained Random Testing

- In a directed test, the coverage points are coded in the test itself

- Test writer must code *each* specific scenario to specify intent explicitly

- Must be able to predict interesting cases in order to code them

- Doesn't scale well

- Randomness inherent in C-R allows unpredicted scenarios to be exercised

- Exposes corner cases the designer may not have considered

- Testbench is an objective description of intent against which to check the design

- Kind of like an independent verification team

- Functional Coverage tells which features were exercised

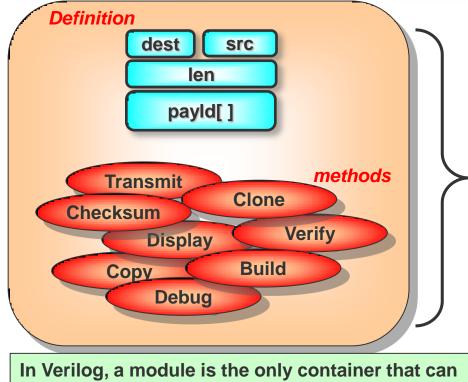

#### **SV-OOP vs. Verilog**

hold both the definition of the packet fields and all the methods needed to manipulate those fields.

In SV, classes are infinitely better suited, because:

- Objects are dynamic, not static

- Create or destroy objects at will

- Classes are inheritable, polymorphic etc.

```

class ether packet extends packet;

// Ethernet Packet Fields

bit[47:0] dest, src;

bit[15:0] len;

bit [7:0] payld [];

// onboard methods

function new(int i);

payld = new[i]; len = i;

endfunction : new

function void display;

$displayh("\t src: ", src);

foreach (payld[i])

$display("payld[i] = %d",i,payld[i]);

endfunction : display

task transmit frame();

. . .

function clone();

. . .

endclass : ether packet

```

#### **Tools and Technology Aren't Enough**

#### EDA sells tools and "materials"

- To build a bookcase, you need to apply the tools and technologies in useful ways

- What we need are Advanced Methodologies

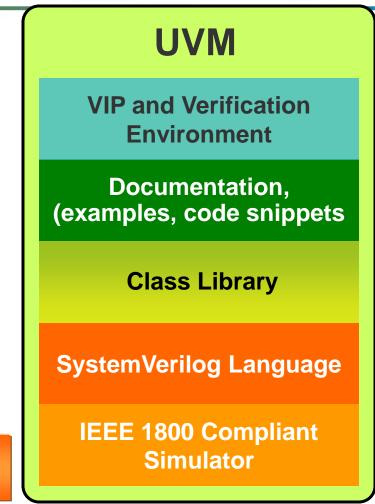

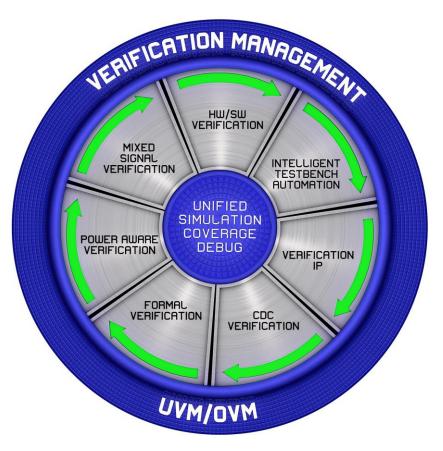

## **Unified Verification Methodology**

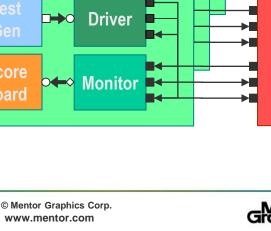

- UVM Open-source framework for reusable verification based on SystemVerilog

- SystemVerilog Class Library

- Set of core building blocks for effective, reusable verification environments

- Library of common services

#### **Interoperability and reuse**

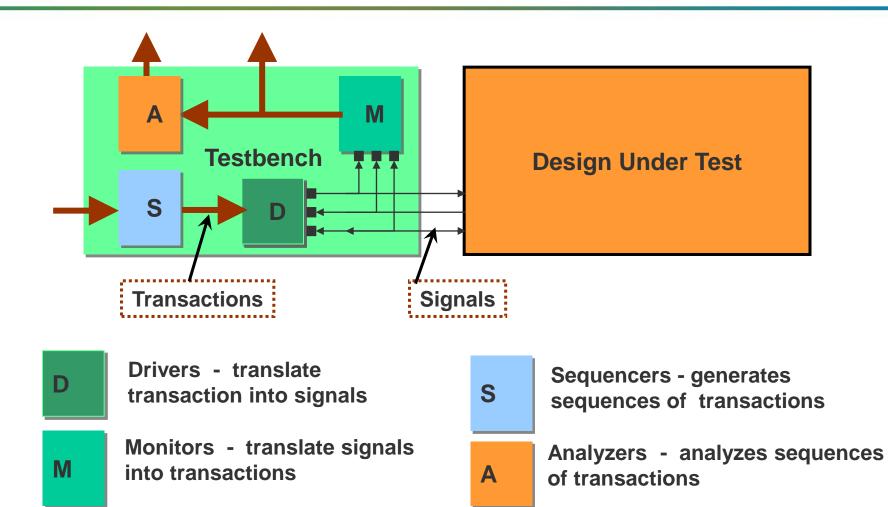

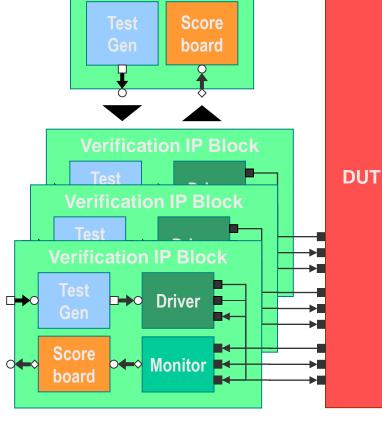

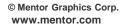

#### **UVM-based Testbench Architecture**

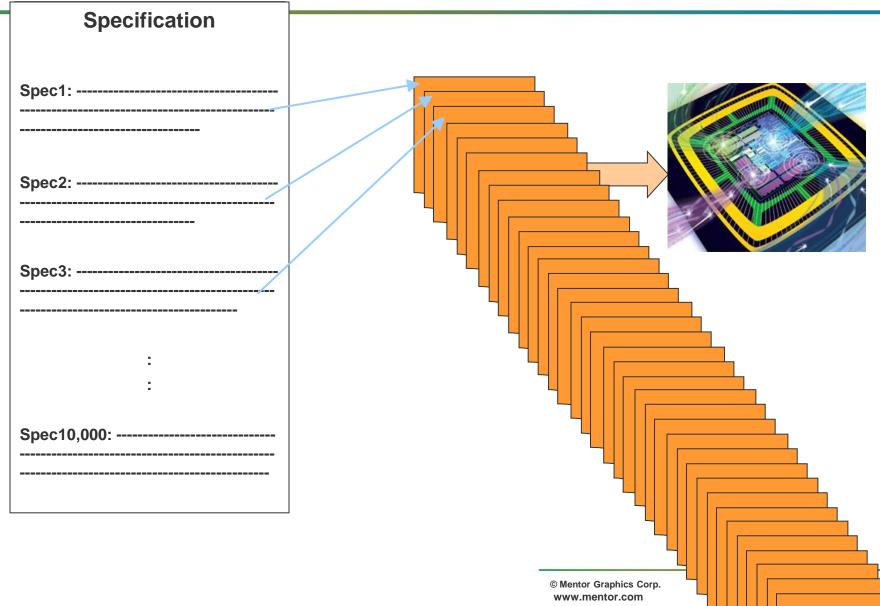

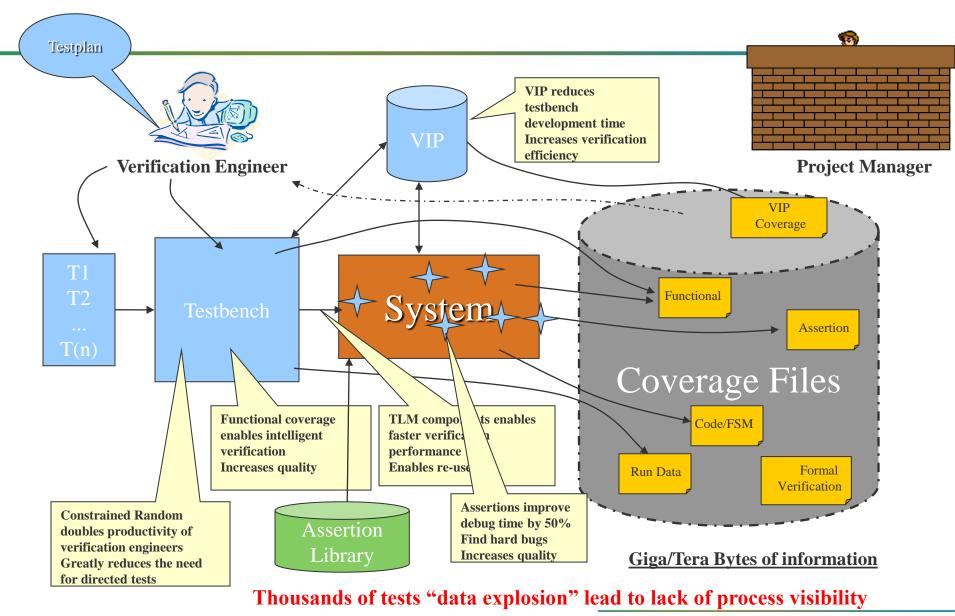

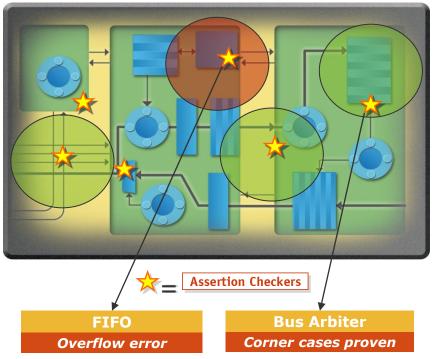

# **Coverage Data Overload**

© Mentor Graphics Corp. www.mentor.com

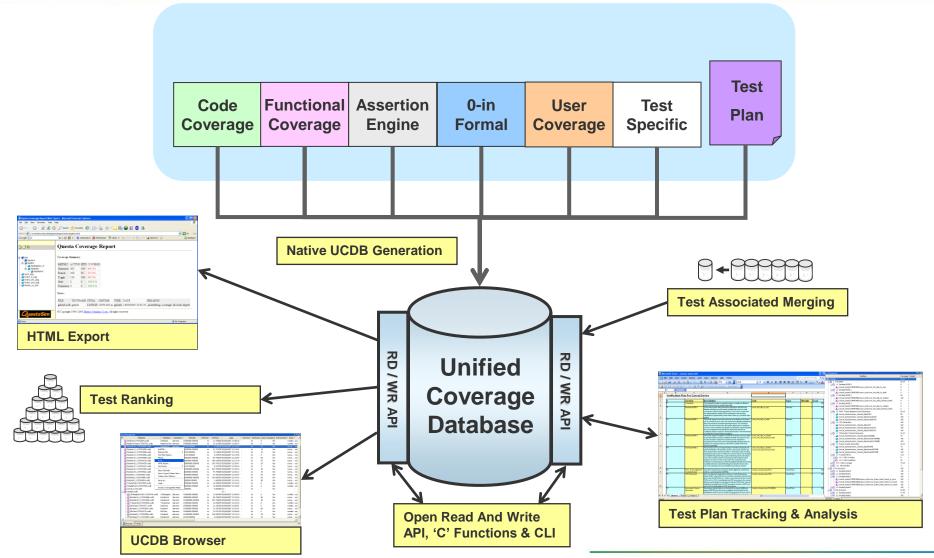

# **Mentor's Unique Advantage**

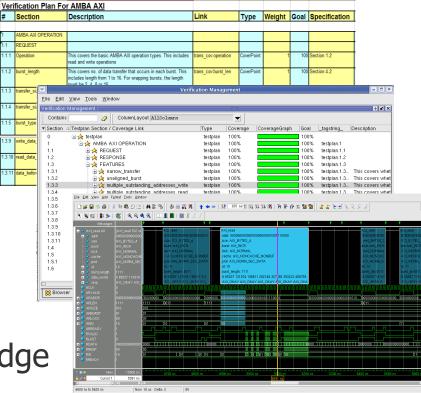

#### **Managing Verification Through Metrics**

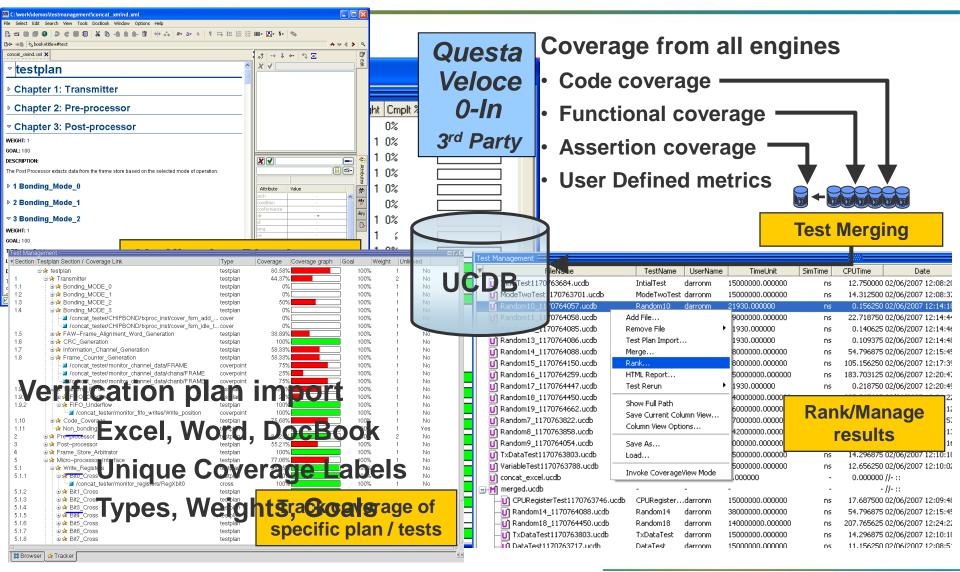

## **When Is Verification Complete?**

|              | Test Mana                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            | <i>***</i>            |      |               |  |

|--------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|------|---------------|--|

| 90% +        | <ul> <li>Section</li> </ul> | Testplan Section / Coverage Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Туре                                                       | Coverage Coverage gra |      | ight Unlinked |  |

|              |                             | 🖃 🐅 testplan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            | 80.58%                | 100% | 1 No          |  |

|              | 1                           | 📮 🐅 Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | testplan                                                   | 44.37%                | 100% | 2 No          |  |

| 80% +        | 1.1                         | 🕀 🖈 Bonding_MODE_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 0%                    | 100% | 1 No          |  |

|              | 1.2                         | 🕀 🚧 Bonding_MODE_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 0%                    | 100% | 1 No          |  |

|              | 1.3                         | Bonding_MODE_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | testplan                                                   | 50%                   | 100% | 1 No          |  |

| <b>'0%</b> + | 1.4                         | 🗟 🚧 Bonding_MODE_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 0%                    | 100% | 1 No<br>1 No  |  |

| 0 /0         |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 'concat_tester/CHIPBOND/txproc_inst/cover_fsm_add cover 0% |                       |      |               |  |

|              |                             | /concat_tester/CHIPBOND/txproc_inst/cover_fsm_idle_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            | 0%                    | 100% | 1 No          |  |

|              | 1.5                         | 🕀 🛠 FAW-Frame_Alignment_Word_Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | testplan                                                   | 38.89%                | 100% | 1 No          |  |

| <b>60%</b> + | 1.6                         | 🗟 🛠 CRC_Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 100%                  | 100% | 1 No          |  |

|              | 1.7                         | 🖶 🛠 Information_Channel_Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 58.33%                | 100% | 1 No          |  |

|              | 1.8                         | ⇒☆ Frame_Counter_Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | testplan                                                   | 58.33%                | 100% | 1 No          |  |

| 50% +        |                             | /concat_tester/monitor_channel_data/FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | coverpoint                                                 | 75%                   | 100% | 1 No          |  |

|              |                             | /concat_tester/monitor_channel_data/chana/FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | coverpoint                                                 | 25%<br>75%            | 100% | 1 No<br>1 No  |  |

|              | 1.9                         | ■ /concat_tester/monitor_channel_data/chanb/FRAME<br>□ ☆ Transmit FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | coverpoint<br>testplan                                     | 62.5%                 | 100% | 1 No          |  |

| <b>10%</b> + | 1.9                         | argentalisting_ricos<br>argentalisting_ricos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | testplan                                                   | 25%                   | 100% | 1 No          |  |

|              | 1.9.2                       | □ ☆ FIFO Underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 100%                  | 100% | 1 No          |  |

|              | 1.9.2                       | /concat_tester/monitor_fifo_writes/Write_position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | coverpoint                                                 | 100%                  | 100% | 1 No          |  |

| 80% +        | 1.10                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | testplan                                                   | 75.68%                | 100% | 1 No          |  |

| 0 /0         | 1.11                        | A Code_coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | testplan                                                   | / 9.00%               | 100% | 1 Yes         |  |

|              | 2                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | testplan                                                   | 81.25%                | 80%  | 2 No          |  |

| 20% +        | 3                           | a ★ Post-processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | testplan                                                   | 55.21%                | 100% | 1 No          |  |

| 20% +        |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | testplan                                                   | 100%                  | 100% | 1 No          |  |

|              | 5                           | ⇒ 🛠 Micro-processor Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | testplan                                                   | 77.06%                | 100% | 1 No          |  |

|              | 5.1                         | Grade Strate | testplan                                                   | 98.15%                | 95%  | 1 No          |  |

| 0% +         | 5.1.1                       | Bit0 Cross                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | testplan                                                   | 100%                  | 100% | 1 No          |  |

|              |                             | J /concat tester/monitor registers/RegXbit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cross                                                      | 100%                  | 100% | 1 No          |  |